# **Soundness of Predictive Concurrency Analyses**

SHUYANG LIU, University of California at Los Angeles, USA DOUG LEA, SUNY Oswego, USA JENS PALSBERG, University of California at Los Angeles, USA

A predictive analysis takes an execution trace as input and discovers concurrency bugs without accessing the program source code. A sound predictive analysis reports no false positives, which sounds like a property that can be defined easily, but which has been defined in many different ways in previous work. In this paper, we unify, simplify, and generalize those soundness definitions for analyses that discover concurrency bugs that can be represented as a consecutive sequence of events. Our soundness definition is graph based, separates thread-local properties and whole-execution properties, and works well with weak memory executions. We also present a three-step proof recipe, and we use it to prove six existing analyses sound. This includes the first proof of soundness for a predictive analysis that works with weak memory.

CCS Concepts: • Software and its engineering  $\rightarrow$  Formal software verification.

Additional Key Words and Phrases: Concurrency, Dynamic Program Analysis, Soundness, Weak Memory Models

#### **ACM Reference Format:**

Shuyang Liu, Doug Lea, and Jens Palsberg. 2025. Soundness of Predictive Concurrency Analyses. *Proc. ACM Program. Lang.* 9, OOPSLA1, Article 101 (April 2025), 44 pages. https://doi.org/10.1145/3720435

#### 1 Introduction

Concurrent programs are often error-prone due to the non-deterministic nature of their executions. Over the last two decades, various techniques have been proposed to catch bugs in concurrent programs. Among them, *dynamic predictive analysis* has become a promising research area. A dynamic predictive analysis takes an execution trace as input and discovers concurrency bugs without accessing the program source code. Recent works in the area of predictive analysis [4–8, 11, 18, 19, 21, 27, 28] support *soundness* as one of their most important properties. A sound predictive analysis reports no false positives, which sounds straightforward but has been defined in many different ways in previous work [8, 11, 18, 19, 21, 25, 27, 28].

Three problems emerge from the use of varying soundness criteria in previous work. First, there is no single recipe for proving soundness, so existing proofs cannot be directly applied or adapted to a new algorithm. Second, some previous proofs later turned out to be flawed when counterexamples emerged, without revealing whether the algorithm or the soundness proof were wrong. Third, existing soundness criteria and proof techniques have no support for weak memory models. This is in part due the focus on trace-based soundness definitions in previous work, which is a poor fit for weak memory models.

To address these issues, we propose a modular framework for soundness of predictive analyses that unifies, simplifies, and generalizes existing approaches and handles weak memory behaviors.

Authors' Contact Information: Shuyang Liu, University of California at Los Angeles, Los Angeles, USA, sliu44@cs.ucla.edu; Doug Lea, SUNY Oswego, Oswego, USA, dl@cs.oswego.edu; Jens Palsberg, University of California at Los Angeles, Los Angeles, USA, palsberg@ucla.edu.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2025 Copyright held by the owner/author(s).

ACM 2475-1421/2025/4-ART101

https://doi.org/10.1145/3720435

Instead of traces, our framework is based on *execution graphs*, which are widely used in the field of axiomatic memory models [1–3, 22, 23]. Compared to traces, execution graphs distinguish the sequential semantics per thread versus global weak memory semantics as two separate aspects of validity. The former is affected by the source language semantics, and the latter is determined by the axiomatic memory model. As a result, this feature enables a modular structure of soundness, which also leads to a simple recipe for constructing a proof.

Our contributions are the following:

- §4 We propose a modular soundness definition parameterized by a memory model. The definition is more general than existing soundness definitions, reflects a closer connection with the language semantics, and can be applied with weak memory models. Specifically, we derive an executability property from a language semantics and augment existing multicopy-atomic memory models with lock semantics. We analyze the execution spaces represented by the existing soundness definitions and explain their relationships with our soundness definition.

- §5 We provide a three-step recipe for constructing a soundness proof by constructing a witness execution graph that satisfies our soundness definition. We also provide a set of reusable lemmas that can be applied in the construction of proofs under other memory models or semantic constraints.

- §6 We use our recipe to prove the soundness of six data race predictive analyses [8, 9, 15, 18, 19, 21]. Among them, the proof for MCR-TSO [9] is the first proof of soundness for a predictive analysis that works with weak memory. In addition, we extend the approach of Huang and Huang [9] and define a new data race predictor based on a transformation that can discover more data races under TSO. We show that the extended data race predictor is sound following the same recipe in Appendix F.

§2 reviews the past works and the soundness definitions they have used; §3 introduces the formal definitions; §7 concludes the paper.

Scope and Limitations. In this paper we focus on the *strong* soundness theorem, i.e., every reported bug indicates a valid execution that witnesses the bug. On the other hand, soundness definitions for data races may be extended to state that every reported data race indicates either the presence of a race or a predictable deadlock, i.e., the *weak* soundness theorem. Our treatment does not currently incorporate the deadlock provision covered by the weak soundness theorem, which is used in some partial-order-based data race predictive analyses [6, 11, 27]. While one can modify our soundness definition with a disjunction to accommodate the weak soundness theorem, precisely capturing a predictable deadlock pattern with respect to the reported data race requires further exploration.

We represent the notion of a bug as a consecutive sequence of events (the formal definition can be found in Section 3). This corresponds to most common definitions of data race errors, but not necessarily to violations of higher-level properties such serializability. We leave as future work techniques for transforming these into forms that are amenable to our approach.

We restrict attention to multicopy-atomic memory models. Extending coverage to non-multicopy atomic models would introduce additional potential executions that are not possible on other platforms. Some well-known multicopy-atomic models include x86-TSO [20], ARMv8 [1, 23], and RISC-V, while ARMv7[17] and the PowerPC [24] models are non-multicopy-atomic. Java and C/C++ have non-multicopy atomic models to provide multi-platform supports. The primary challenge in accommodating non-multicopy-atomic models is integration with the semantics of lock operations, which we leave as future work. Further, we omit Read-Modify-Write (RMW) operations. Accommodating them would add some cases to our soundness definition. Adopting these restrictions allows us to omit coverage of issues that add complexity without bearing on the basic logic of our approach.

| Name           | Memory<br>Model | Bug Type                                 | Sound Witness Definition                                 | Ref.    |

|----------------|-----------------|------------------------------------------|----------------------------------------------------------|---------|

| HB (FASTTRACK) | SC              | Data Race                                | Correct Reordering                                       | [5, 15] |

| CP             | SC              | Data Race                                | Correct Reordering                                       | [27]    |

| WCP            | SC              | Data Race                                | Correct Reordering                                       | [11]    |

| SHB            | SC              | Data Race                                | Relaxed CR                                               | [18]    |

| SyncP          | SC              | Data Race                                | Sync-Preserving CR                                       | [19]    |

| SPD            | SC              | Deadlock                                 | Sync-Preserving CR                                       | [28]    |

| OSR            | SC              | Data Race                                | Optimistic CR                                            | [26]    |

| M2             | SC              | Data Race                                | Correct Reordering                                       | [21]    |

| RVPredict      | SC              | Data Race                                | Feasible Closure                                         | [8]     |

| SeqCheck       | SC              | Bugs represented as a sequence of events | Feasible Closure                                         | [4]     |

| MCR-TSO        | TSO             | Data Race                                | Correct Reordering informally relaxed with TSO semantics | [9]     |

Fig. 1. Various Criteria for a Sound Witness from Past Work

*Acknowledgement.* We thank the anonymous reviewers for helping to clarify limitations and opportunities for future work. This material is based upon work supported by the National Science Foundation under Grant No. 1815496.

#### 2 Motivation

A concurrency bug is a sequence of events that occur in some specific order. For example, a *data race* is a pair of two conflicting events ordered consecutively. Since a predictive analysis predicts whether a bug can occur in some execution of the program that produced the input execution, the soundness theorem of an analysis is defined by the existence of a *witness* execution that exhibits the bug. Therefore, characterizing the valid witness executions and showing that each reported bug corresponds to a witness execution that satisfies all the characteristics become critical in the soundness proofs of existing works in predictive analysis. Fig. 1 shows a summary of the soundness criteria used in existing works.

FASTTRACK [5] is a data race analysis that builds a partial order, the *happens-before* (HB) order [15], among the events in a given input trace. While FASTTRACK with HB can report multiple data races in a single run, only the first data race is guaranteed to be sound. The soundness theorem of FASTTRACK states that the algorithm correctly implements the HB order using vector clocks. On the other hand, the soundness of the HB order was assumed in the paper.

After FastTrack, CP [27] and WCP [11] built weaker partial orders than HB and used Correct Reordering (CR) to characterize valid witness traces. Correct Reordering requires each read event that appears in the witness execution to maintain the same values as in the input execution. The soundness theorems of both algorithms state that the first race reported by the algorithms is a HB-race or there is a deadlock in a correct reordering of the input trace. Both the soundness of Correct Reordering and the HB order were implicitly assumed.

Mathur et al. [18] shows an improvement over HB that ensures the soundness of *all* reported data races. Their idea is to build a strictly stronger partial order, *schedulable-happens-before* (SHB), which orders the unsound HB-races after the first race, so that all reported data races are sound. The soundness of SHB is based on a relaxed version of Correct Reordering, denoted as Relaxed

CR in Fig. 1. Relaxed CR has the same requirements of Correct Reordering except that if a read is the last event of a thread in the witness execution, then it does not have to maintain the same value. In addition to the soundness of SHB, Mathur et al. [18] also formally proved that HB is sound under the definition of Relaxed CR. But the soundness of Relaxed CR and Correct Reordering were implicitly assumed.

Mathur et al. [19] and Tunç et al. [28] used a more restricted version of Correct Reordering called Sync-Preserving CR. In addition to the requirements of Correct Reordering, the critical sections that appear in a Sync-Preserving CR follow the same synchronization order as in the input trace. The proofs of both works were done by linearizing an event closure called SRFClosure (or SPClosure in [28]) using the same trace order of the input trace. The soundness of Sync-Preserving CR relied on Correct Reordering, which was implicitly assumed.

Shi et al. [26] used Optimistic CR, which relaxes the notion of Sync-Preserving CR to capture a slightly different set of data races. Comparing to Sync-Preserving CR, Optimistic CR allows certain critical sections to be reordered. On the other hand, since the Optimistic lock-closure sometimes includes more events than the Sync-preserving closure, as demonstrated in their example [26, Example 7], Optimistic CR and Sync-Preserving CR are not comparable in general. Similar to Sync-Preserving CR, the soundness of Optimistic CR relied on Correct Reordering, of which the correctness was implicitly assumed.

Pavlogiannis [21] used Correct Reordering as the soundness criteria for a witness trace. The algorithm computes a partial order P over a subset of events from the input trace and used it to determine if a pair of events forms a data race. The key correctness result is their Theorem 3.1, which showed that for a trace-closed partial order P computed from the input trace, the Max-Min algorithm that solves a particular linearization problem based on P always produce a correct reordering [21, Theorem 3.1]. But the soundness of Correct Reordering was implicitly assumed.

Huang et al. [8] used the notion of Feasible Closure of traces derived from the causal model of ŞerbănuŢă et al. [25]. Their main correctness result [8, Theorem 1] showed the existence of a mapping from symbolic feasible traces to concrete feasible traces, but did not formally show that the set of concrete feasible traces can be generated by the same program of the input trace.

Similarly, although with a different approach to pretict concurreny bugs, Cai et al. [4] developed SeqCheck using Feasible Closure as their correctness criteria as well. The main soundness theorem [4, Theorem 1] stated that their algorithm returns a trace that is an element of the Feasible Closure given the input trace. The proof was done by induction on the structure of the trace that is produced by their algorithm and showing that it has the same structure as a trace in the Feasible Closure.

Huang and Huang [9] used a restricted version of Feasible Closure that preserves all read values, but relaxed with a memory operation constraint,  $\Phi_{mem}$ , to capture the weak behavior under x86-TSO. Effectively, their soundness criteria is the same as Correct Reordering relaxed with the TSO write-buffer semantics. Instead of requiring all program orders to be preserved, it does not require write-to-read program orders to be preserved. However, the soundness of the constraints was left unproved.

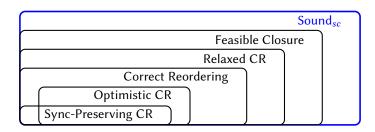

From the review above, we can see that the soundness criteria from existing works all specify properties that a witness execution has to satisfy given an input execution. For dynamic predictive analyses, the program source code is kept unknown. Therefore, all existing soundness definitions focus on characterizing a set of valid executions that can be produced by *all* programs that can generate the input execution. In other words, existing soundness definitions focus on executions in an *intersection* space of all the programs that can generate the input execution. Fig. 2 shows a hierarchy of the sets of valid executions specified by the soundness criteria from past works. Each rectangle represents a set of executions that satisfy the corresponding soundness definition.

Fig. 2. Hierarchy of Existing Sound Definitions under Sequential Consistency

However, since all existing definitions focus on an intersection execution space, the size of this execution space depends on the amount of information about the program semantics captured in the input execution. Indeed, the analyses that used Feasible Closure [7, 8, 25] record branch events in the input execution whereas other analyses [11, 18, 19, 21, 27, 28] do not. This difference enables Feasible Closure to subsume other soundness definitions in Fig. 2. A better approach is to define soundness independently of how much information the input execution captures. We focus on characterizing the set of valid executions that can be produced by a single program that generates the input execution. In other words, our soundness definition is *not based on an intersection* of execution sets, but is based on the complete execution set of each program that generates each input execution. Obviously, this set of executions subsumes all other sets specified by existing definitions, and is shown as the blue rectangle in Fig. 2 annotated with Sound<sub>sc</sub>. The set inclusion relations shown in Fig. 2 is the following.

```

Sound<sub>sc</sub> [this paper] \supseteq Feasible Closure [8]

\supseteq Relaxed CR [18]

\supseteq Correct Reordering [11, 21, 27]

\supseteq Sync-Preserving CR [19, 28]

```

The subscript sc in the name of our soundness stands for sequential consistency. While sequential consistency is subsumed by other memory models, the sets of valid executions under different memory models are not comparable in general. In §4, we give a general definition of soundness, Sound<sub> $\mathcal{M}$ </sub>, under a memory model  $\mathcal{M}$ .

The dynamic nature of the analyses, that is, having no access to the program source code, makes this set of executions unknown to the analysis tools. As a result, the traditional approach, which requires one to step through the source code of the program to show an execution is valid, cannot be used to prove a predictive analysis sound. Instead, we leverage the existing input execution and provide a three-step proof technique in Section 5. Note that the restriction of having no access to the program source code does not affect the soundness definition, but only the proof technique.

In Appendix A, we provide the formal definitions of the existing soundness criteria and show their relationships with our soundness definition.

#### 3 Preliminaries

In this section, we recall standard definitions of programs and execution graphs [22], which we extend with acquire and release events [21], and a straightforward sync order over such events. Our operational semantics of programs uses the standard notion of a thread state (Definition 3). We instrument thread states with symbolic book-keeping information that plays no role in the semantics but helps in proofs of soundness.

We use standard notation for relations and functions. For a relation R, we use  $R^{?}$ ,  $R^{+}$ , and  $R^{*}$  to denote the reflexive, transitive, and reflexive-transitive closures of R, respectively. We use  $R^{-1}$  for

```

i \in \operatorname{Instr} ::= r := e x \in \operatorname{Loc} v \in \operatorname{Val} v \in \operatorname{Val} v \in \operatorname{Instr} = e v \in \operatorname{Reg} v \in \operatorname{Reg} v \in \operatorname{Instr} = e v \in \operatorname{Instr} =

```

Fig. 3. Instructions of the Language

the inverse of R. Given a set A, [A] is the identity relation on A,  $\wp(A)$  is the power set of A. The composition of two relations  $R_1$  and  $R_2$  is written as  $R_1$ ;  $R_2$ .  $R|_A$  stands for R restricted to the set A. We say a set A is downward-closed with respect to a relation R if for each element  $e \in A$ , if there is  $\langle e', e \rangle \in R$ , then  $e' \in A$ . We use the following domains: Loc is a set of shared memory locations; Lock is a set of locks; Val is a set of concrete integer values; Sym is a set of symbols; Reg is a set of thread-local registers; and Thrd is a set of natural numbers for thread identifiers. In addition, we assume all memory locations are fixed.

### 3.1 Programs

A concurrent program consists of a set of threads, each containing a list of instructions. Formally, a *program* is a map from thread identifiers to sequential programs  $P: \mathsf{Tid} \to \mathsf{Sprog}$ , where  $\mathsf{Sprog} = \mathbb{N} \to \mathsf{Instr}$  and the set of instructions is defined in Fig. 3.

Our sequential programs use standard instructions, including lock and unlock instructions for the acquire and release operations of locks. These two instructions allow us to reason about lock operations without worrying about the implementations of locks. We assume the implementation of lock and unlock is correct and guarantees lock-fairness [13, 16] so that each lock-acquiring request is eventually fulfilled. As a result of this assumption, the set of lock events generated from the lock instructions is definite.

#### 3.2 Execution Graphs

Each program generates a set of *execution graphs*. In this section, we formally define events and execution graphs.

An *event* is a tuple of form  $\langle tid, eid, typ, val, loc \rangle$  where  $tid \in \mathbb{N}$  is the identifier of the thread of the event;  $eid \in \mathbb{N}$  is a unique identifier for the event;  $typ \in \{r, w, \text{acq}, \text{rel}, \text{br}\}$  is the event type with r standing for read events, w for write events, acq for lock acquire events, rel for lock release events, and br for branch events;  $val \in \text{Val}$  is the value of the event; and  $loc \in \text{Loc} \cup \text{Lock}$  is the memory location or lock that the event accesses.

An execution graph consists of a set of events and the relations over the events.

Definition 1 (Execution Graph). An *execution graph*  $G = \langle \text{Evt}, \text{po}, \text{rf}, \text{co}, \text{sync} \rangle$  with each component defined below:

- Events is a finite set of events G.Evt. We use G.T where  $T \in \{Rd, Wrt, Acq, Rel, Br\}$  to denote subsets of events based on their types. In addition, G.Init is a set of initialization writes to each memory location. G.Init  $\cap G$ .Evt  $= \emptyset$ .

- Program Order (po) is a partial order  $G.po \subseteq G.Evt \times G.Evt$ .  $\langle e_1, e_2 \rangle \in G.po$  iff  $e_1.tid = e_2.tid$  and  $e_1.eid < e_2.eid$ .

- Reads-from Order (rf) is a binary relation  $G.rf \subseteq G.Wrt \times G.Rd$ .

- Coherence Order (co) is a binary relation  $G.co \subseteq G.Wrt \times G.Wrt$ .

- Synchronization Order (sync) is a binary relation G.sync  $\subseteq G$ .Rel  $\times G$ .Acq.

In addition, the from-read order [3] (fr) is defined as  $fr = rf^{-1}$ ; co. We use com to denote the union of the communication orders, com =  $fr \cup rf \cup co$ . If an execution graph is sequentially consistent, then there is also a linear order trace among all events of the execution graph. For each event e, we use LocksHeld(e) to denote the set of locks that are acquired but not released at the point of e in its thread.

Furthermore, a *symbolic execution graph*  $\hat{G}$  is an execution graph with an event set of which event values are either concrete values  $v \in \text{Val}$  or symbols  $\hat{s} \in \text{Sym}$ . For each read event  $r \in \hat{G}$ .Rd, if r is a read event with a concrete value, then either there exists a unique concrete write event  $\langle w, r \rangle \in \hat{G}$ .rf such that w.loc = r.loc and w.val = r.val, or r.val is the initial value. Note that for a read event with symbolic value, we do not require it to be mapped to a unique write event. Intuitively, symbolic execution graphs are used to accommodate the approaches of Huang et al. [8] and Huang and Huang [9], where some of the events becomes symbolic due to changes of the rf-map in the prediction result. On the other hand, later in Section 5.3, we show that there exists a concrete execution graph that a symbolic execution graph can be mapped to, given a set of conditions are satisfied.

Using definitions from [22], an execution graph G is a *plain* execution graph, if  $G.rf = G.co = G.sync = \emptyset$ . An execution graph G with well-formed rf, co, and sync relations is called a *complete* execution graph.

DEFINITION 2 (Well-formed Complete Execution Graph). A complete execution graph G = (Evt, po, rf, co, sync) is well-formed if

- Each read event must be justified by a write event in the same execution graph. That is, for each read event  $r \in G$ .Rd either there is a unique write event  $w \in G$ .Wrt such that  $\langle w, r \rangle \in G$ .rf, or  $r.val = w_{init}.val$  where  $w_{init}$  is the initialization write of r.loc. For each pair  $\langle w, r \rangle \in G$ .rf, r.val = w.val, and r.loc = w.loc.

- For each pair of distinct writes  $w_1$  and  $w_2$ , if  $w_1.loc = w_2.loc$ , then either  $\langle w_1, w_2 \rangle \in G.$ co or  $\langle w_2, w_1 \rangle \in G.$ co but not both. In addition,  $\langle w_0, w \rangle \in G.$ co for each initial write  $w_0$  and  $w \in G.$ Wrt such that  $w_0.loc = w.loc$ .

- There is a function match :  $G.Rel \rightarrow G.Acq$  such that for each  $rel \in G.Rel$ , match(rel).loc = rel.loc, and  $\langle match(rel), rel \rangle \in G.po$ . There is a function  $Open : G.Lock \rightarrow G.Acq$  such that Open(l) = acq iff acq.loc = l and for all  $rel \in G.Rel$ ,  $match(rel) \neq acq$ . If no such acquire event exists for lock = l. For each  $\langle rel, acq \rangle \in G.sync$ , rel.loc = acq.loc. For each lock = lock, lock

# 3.3 From Programs to Execution Graphs

Given the formal definitions of programs and execution graphs, we explain how execution graphs are generated from programs.

An execution graph is generated from a program by starting with an empty execution graph  $G_0$ . Given a value map  $loadVal : Load \rightarrow Val$  for each load instruction of the form r := [x], use the sequential operational semantics of instructions and the loadVal() function to generate a chain of events for each thread by adding one event at a time. At this stage, only the program order po is added to the graph while other relations are left empty. The result of this stage is a plain execution graph. Note that we do not consider the consistency of the graph at this stage. Lastly, rf, co, and sync relations are added to the plain execution graph according to the values and

Fig. 4. Symbolic Expressions

the well-formedness conditions, which we will define later. The result of this stage is a complete execution graph ready for the consistency check.

We next define the notion of thread state. Here we use the same definition from [22] with an additional *symbolic* register state  $\Phi^{\theta}$  and a function  $\theta:G.Rd \to Sym$ . These two new components do *not* replace any functionality of other components as described in Podkopaev et al. [22]. They are only added for additional book-keeping purposes. Later in the proof of Lemma 1 in §4.3, they are used to re-construct state transition paths of prediction results.

In addition, we assume memory fairness [13] so that each lock (l) instruction will eventually succeed and produce an acq event.

Definition 3 (Thread State). A thread state  $st \in State$  for a thread t is a tuple

$$st = \langle sprog, pc, \Phi, G, \Psi, ctrl, \theta, \Phi^{\theta} \rangle$$

with each component defined as follows:

- $sprog : \mathbb{N} \to Instr$  is the instructions in thread t, sprog = P(t).

- $pc \in \mathbb{N}$  is the program counter pointing to the next instruction

- $\Phi : \mathsf{Reg} \to \mathsf{Val}$  is map recording the value of each register

- G is the execution graph that has been constructed so far for thread t

- $\Psi$  : Reg  $\rightarrow \wp(G.Rd)$  maps each register to a set of read events in G such that the value in the register depends on the set of reads.

- $ctrl \subseteq G$ .Rd is a set of read events that has a control dependency with the current program point.

- θ: G.Rd → Sym is a map recording the symbolic value of each read event. When a read

event is generated from executing a load instruction, in addition to the concrete value that it

receives via the loadVal function, a fresh new symbol is assigned to the read event and an

entry is added in θ.

- $\Phi^{\theta}$ : Reg  $\to$  SymExpr is a map recording the symbolic expression used to calculate the current (concrete) value on each register. The grammar of symbolic expressions is defined in Fig. 4. In other words, the concrete value on each register can be calculated by plugging the concrete values of the read events into its symbolic expression.

The initial state for a thread  $t \in \mathsf{Tid}$  is  $st_0^t = \langle sprog, 0, \lambda r. 0, G_0, \lambda r. \emptyset, \emptyset, \lambda rd. null, \lambda r. 0 \rangle$  where sprog = P(t) and  $G_0$  is an empty execution graph such that  $G_0.\mathsf{Evt} = G_0.\mathsf{po} = G_0.\mathsf{rf} = G_0.\mathsf{co} = G_0.\mathsf{sync} = \emptyset$ .

An important invariant for a state to be valid is  $\forall r \in \text{Reg}$ ,  $subst(\Phi^{\theta}(r), val^{\theta}(\Psi(r))) = \Phi(r)$  where the helper functions  $subst: \text{SymExpr} \to (\text{Sym} \to \text{Val}) \to \text{Expr}$  replaces each symbol in an symbolic expression with a concrete value given a mapping from symbols to concrete values, and  $val^{\theta}: \wp(G.\text{Rd}) \to (\text{Sym} \to \text{Val})$  uses  $\theta$  to provide a set of such mapping. In words, evaluating the symbolic expressions that each register is mapped to with the concrete value of each read events should have the same result as the value stored in  $\Phi$ . Note that in order for this invariant to hold, a register cannot occur on both sides of an assignment.

For two thread states  $st_1, st_2 \in S$ tate of a thread t, we write  $st_1 \to_t st_2$  if  $st_1$  steps to  $st_2$  in a single step and  $st_1 \to_t^* st_2$  if  $st_1$  steps to  $st_2$  in zero or more steps. We provide the sequential operational semantics for our language in Appendix B.

We borrow the following definition from [22]. For an execution graph G and  $t \in Tid$ ,  $G|_t$  is a thread of events such that  $G|_t$ . Evt = G. Evt $|_t$ ,  $G|_t$ .po = G.po  $\cap$  ( $G|_t$ . Evt  $\times$   $G|_t$ . Evt), and  $G|_t$ .rf =  $G|_t$ .co =  $G|_t$ .sync =  $\emptyset$

DEFINITION 4 (PLAIN PROGRAM EXECUTIONS [22]). An execution graph G is an execution graph of a program P if for every  $t \in \mathsf{Tid}$ , there exists a state st such that  $st.G = G|_t$  and  $st_0^t \to_t^* st$ .

We write  $G \in \llbracket P \rrbracket$  for such an execution graph G and program P. We say a plain symbolic graph  $\hat{G} \in \llbracket P \rrbracket$  if there exists a  $st_0 \to_t^* st_n$  transition path for each thread t that produces the resulting graph. The only difference from Definition 4 is the invariant condition that each state has to maintain because  $val^{\theta}(\Psi(r))$  may not be defined for every register in the presence of events with symbolic values. We relax the requirement and let the invariant condition only apply to registers with concrete values, i.e.,  $subst(\Phi^{\theta}(reg), val^{\theta}(\Psi(reg))) = \Phi(reg)$  if  $\Phi(reg) \in Val$ . Moreover, if a write event has a concrete value, it has to be computed from concrete values as well. In other words, for each state  $st_i$  such that  $st_i.sprog(st_i.pc) = [x] := e$ , if w is the write event emitted after  $st_i$  and  $w.val \in Val$ , then for each  $reg \in Reg$  used in e,  $\Phi(reg) \in Val$ .

Given a plain execution graph, the rf, co, and sync relations are added to the graph according to Definition 2 to obtain a complete execution graph.

# 3.4 Bug Sequence

Each instance of bug is represented as a sequence of events:

$$b = e_1 \dots e_n$$

The basic well-formedness requirement for a bug sequence is for it to be sequentially consistent. We give three common examples below.

*Data Races.* In the context of *data race* prediction, each reported bug is in the form of a sequence  $e_1e_2$  such that  $e_1.tid \neq e_2.tid \land e_1.loc = e_2.loc \land \{e_1.typ, e_2.typ\} \cap \{Wrt\} \neq \emptyset$ . We write  $e_1 \bowtie e_2$  for such pair of events. Note that the value of  $e_1$  or  $e_2$  may not be the same as occurred in the input execution  $G_{\sigma}$ .

Deadlocks. In the context of deadlock prediction, Tunç et al. [28] provided a necessary pattern consisting a set of acquire events that imposes a cyclic resource dependency. However, note that this pattern itself violates memory consistency because a lock cannot be acquired again while it is held. The essential issue here is that the acquire events in a sound execution represent successful aquisition of the locks, whereas the acquire events in the deadlock pattern of [28] represent requests of the locks. Therefore, for deadlock prediction, the lock request events have to be distinguished from lock acquire events, following the approach of Kalhauge and Palsberg [10]. The rest of the definition stays the same as in [28]. A bug sequence of size k is defined as a sequence of request events  $e_0, \ldots, e_{k-1}$  on k distinct threads  $t_0, \ldots, t_{k-1}$  and k distinct locks  $l_0, \ldots, l_{k-1}$  such that  $e_i.tid = t_i, e_i$  is a request of lock  $l_i$ , where  $l_i \in \text{LocksHeld}(e_{(i+1)\%k})$ . In addition, LocksHeld $(e_i) \cap \text{LocksHeld}(e_j) = \emptyset$  for  $i \neq j$ . Note that using this definition, the composition of a sound witness execution and the deadlock sequence is still a sound execution.

Atomicity Violations. Atomicity violation patterns can be represented as sequences of events in multiple ways. Each pattern consists of an atomic pair, i.e., a pair of events  $(e_1, e_2)$  on the same thread that is expected to be executed atomically, and a third event  $e_3$  accessing the same memory location from another thread. Huang et al. [7] provided one pattern in their example:  $r_1w_1w_2$  where  $r_1 \in \text{Rd}, w_1, w_2 \in \text{Wrt}, r_1.loc = w_1.loc = w_2.loc$ , and  $\langle r_1, w_2 \rangle$  is an atomic pair. Cai et al. [4] provided another example:  $w_2w_1r_1$  where  $\langle w_2, r_1 \rangle$  is an atomic pair.

#### 4 Soundness

We begin this section by asking a question.

What does it mean for a predictive analysis to be sound?

A sound predictive analysis only reports a bug if it can be exposed by a valid witness execution. As shown in Fig. 5, let P be a program with a reported bug to be fixed.  $G_{\sigma}$  is an execution graph of Pcaptured from running P. In the rest of this paper, we assume the captured  $G_{\sigma}$  is sequentially consistent and the events of  $G_{\sigma}$  all have concrete values. A predictive analysis algorithm analyzes  $G_{\sigma}$

Fig. 5. Predictive Analyses

without inspecting P to spot the existence of any concurrent bug. Note that the predictive analysis can report bugs that are not necessarily exposed in the recorded execution  $G_{\sigma}$ , but in some other execution of the same program P. Let  $G_{\rho}$  be such a *witness* execution where the bug is exposed. Then a sound predictive analysis should ensure that  $G_{\rho}$  is indeed a valid execution of P. But what does it mean for an execution to be valid?

We identify two important but separate aspects in answering this question:

- Executability The program that generates the input execution must be able to generate the witness execution. From Definition 4, we can see that this is a *local* property. That is, an execution can be generated by a program if each of its threads can be generated by the program. In an execution graph, threads are formed by events related by the program orders po. In other words, executability means the events on each thread can be generated by the program in the order specified by po.

- **Memory Consistency** Another factor is the memory consistency model under which the execution is executed. Axiomatic memory models specify consistent executions under weak memory contexts by characterizing the ordering relations among the events, including the inter-thread communications. Therefore, this is a *global* property that concerns the orders among the events in an execution graph.

In addition, the well-formedness of the witness and its relationship with the reported bug are required to ensure that the composition of the witness with the reported bug sequence is a sound execution. As a result, we define the overall soundness of a predictive analysis as a conjunction of four major components.

Formally, a predictive analysis is a function Predict :  $\mathcal{G} \to \wp(\mathcal{B})$  that takes a recorded execution as an input and reports a set of bugs predicted from the execution. Soundness of such a predictive analyses is defined as the following.

Sound<sub>$$\mathcal{M}$$</sub>  $\triangleq \forall P \in \text{Prog}, \ \forall G_{\sigma} \in \llbracket P \rrbracket \land \text{SC-consistent}(G_{\sigma}), \ \forall b \in \text{Predict}(G_{\sigma}),$

$$\exists G_{\rho}, \ G_{\rho} \rhd b \land \text{wf}(G_{\rho}) \ \land \ G_{\rho} \in \llbracket P \rrbracket \ \land \ \mathcal{M}\text{-consistent}(G_{\rho})$$

The above soundness definition states that in order to prove a predictive analysis is sound, one needs to show that for each bug reported, there is a *witness* execution  $G_{\rho}$  such that:

| §4.1 $G_{\rho} \triangleright b$             | $G_{\rho}$ is composable with the reported bug $b$ | [Definition 6] |

|----------------------------------------------|----------------------------------------------------|----------------|

| $\S4.2 \text{ wf}(G_{\rho})$                 | $G_{\rho}$ is well-formed                          | [Definition 7] |

| $\S 4.3 \ G_{\rho} \in [\![P]\!]$            | $G_{\rho}$ is executable                           | [Definition 4] |

| §4.4 $\mathcal{M}$ -consistent( $G_{\rho}$ ) | $G_{\rho}$ is $\mathcal{M}$ -consistent            | [Definition 9] |

The first three parts of the conjunction states properties that the witness execution must satisfy as a *plain* execution graph, whereas the last part is about the orders among the events in the witness

execution as a *complete* execution graph. In the rest of this section, we discuss each part in detail. The proofs of the propositions and lemmas can be found in the Appendix C.

# 4.1 Composability with bug sequences

Intuitively, witness  $G_{\rho}$  is the execution that must occur before the bug sequence b occurs. Hence, the composition of them should also be a valid execution. We start by formally defining the composition of an execution graph with an event sequence.

Definition 5 (Composition). Let  $G_{\rho}$  be a well-formed execution graph and b be a bug sequence. Then the composition

$$G = G_o \circ b$$

is an execution graph such that:

- $G.Evt = G_{\rho}.Evt \cup b.Evt$

- $G.po = G_{\rho}.po \cup b.po \cup \{\langle e_1, e_2 \rangle \mid e_1 \in G_{\rho}.Evt \land e_2 \in b.Evt \land e_1.tid = e_2.tid\}$

- $G.co = G_{\rho}.co \cup b.co \cup \{\langle w_1, w_2 \rangle \mid w_1 \in G_{\rho}.Wrt \land w_2 \in b.Wrt \land w_1.loc = w_2.loc\}$

- $G.rf = G_{\rho}.rf \cup b.rf \cup \{\langle w,r \rangle \mid r \in b.Rd \land r \notin range(b.rf) \land w \in G_{\rho}.Wrt \land (\forall w' \in G_{\rho}.Wrt, (w'.loc = w.loc \land w' \neq w) \Rightarrow \langle w', w \rangle \in G_{\rho}.co) \land w.loc = r.loc \land w.val = r.val\}$

- $G.sync = G_{\rho}.sync \cup b.sync \cup \{\langle rel(l), acq(l) \rangle \mid rel(l) \in G_{\rho}.Rel \land acq(l) \in b.Acq\}$

To ensure that the composition  $G_{\rho} \circ b$  is executable, we require  $G_{\rho}$  to be *composable* with the bug sequence b.

Definition 6 (Composability). Let  $G_{\sigma}$  be an input execution that is sequentially consistent,  $G_{\rho}$  be a witness execution with an event map  $\delta_{\rho}:G_{\rho}$ . Evt  $\to G_{\sigma}$ . Evt, and b be a well-formed bug sequence with an event map  $\delta_b:b$ . Evt  $\to G_{\sigma}$ . Evt.

We say an execution graph  $G_{\rho}$  witnesses a bug sequence b, written  $G_{\rho} \triangleright b$ , if  $G_{\rho}$ . Evt  $\cap b$ . Evt =  $\emptyset$  and

- No Skipping. For each thread  $t \in b$ . Thrd, let  $e \in b|_t$ . Evt be the first event occur in  $b|_t$ . For any  $e' \in G_{\sigma}$ . Evt such that  $\langle e', \delta_b(e) \rangle \in G_{\sigma}$ . po, there is an event  $e'' \in G_{\rho}$ . Evt such that  $\delta_{\rho}(e'') = e'$ , and

- Same Control Flow. For each  $r \in G_{\rho}$ .Rd and  $e \in b$ .Evt, if  $\langle \delta_{\rho}(r), \delta_{b}(e) \rangle \in G_{\sigma}$ .ctrl, then  $\delta_{\rho}(r) = r$ .

The conditions above ensure the composition  $G_{\rho} \circ b$  inherits executability from  $G_{\rho}$ .

PROPOSITION 1. Let  $G_{\rho}$  be a well-formed execution graph such that  $G_{\rho} \in [\![P]\!]$ , and b be a bug sequence. If  $G_{\rho} \triangleright b$ , then  $(G_{\rho} \circ b) \in [\![P]\!]$ .

On the other hand, M-consistency (which will be defined in §4.4) is inherited by construction.

Proposition 2. Let  $G_{\rho}$  be a well-formed execution graph such that  $G_{\rho}$  is  $\mathcal{M}$ -consistent, and b be a sequence of events. Then  $(G_{\rho} \circ b)$  is  $\mathcal{M}$ -consistent.

## 4.2 Well-formedness of Plain Execution

The second requirement is well-formedness requirements for a plain execution (Evt, po).

Definition 7 (Well-Formed Plain Execution). A plain execution  $G_{\rho}=(\text{Evt},\text{po})$  is well-formed if:

•  $G_{\rho}$  po is a partial order over Evt that orders each pair of events  $\langle e_1, e_2 \rangle$  iff  $e_1.tid = e_2.tid$ .

- Read Feasible. For each read event included in  $G_{\rho}$ . Evt, either there exists a write event included in  $G_{\rho}$ . Evt with the same value and location, or the value of the read is the same as the initial value of the memory location.

- Lock Feasible. For each lock  $l \in \text{Lock}$ , there is at most one open critical section protected by l. An open critical section is defined as sequence of events totally ordered by  $G_{\rho}$ , po where the minimal event in the sequence is an acquire event acq(l) for some lock l and the matching release event rel(l) is not included in  $G_{\rho}$ . Evt.

# 4.3 Executability

Now we turn our attention to the most important part of the soundness definition, *executability*. Given a witness execution graph  $G_{\rho}$ , we want to make sure that  $G_{\rho}$  is indeed an execution graph of the input program P, namely,  $G_{\rho} \in [\![P]\!]$ , via the semantics defined in Appendix B.

Typically, in order to show that an execution graph  $G_{\rho}$  is generated by a program P, one must start from the initial state (as seen in §3) and determine whether there is a reachable state containing  $G_{\rho}$  from the initial state via a path of transitions. However, in the setting of dynamic analysis, one cannot inspect the source code of P and hence cannot follow the semantic rules to determine whether such a state is reachable.

In the setting of dynamic analysis, what we have is the input execution  $G_{\sigma}$ , which is obtained by running the program P, i.e.,  $G_{\sigma} \in \llbracket P \rrbracket$ . Therefore, for each thread t in  $G_{\sigma}$ , there exists a path  $st_0 \to st_1 \to \ldots \to st_k$  with each  $st_i \in S$ tate and  $st_0.sprog = P(t)$ . We use  $Path(G_{\sigma}|_t)$  to denote this path. Again, due to the nature of dynamic analyses, the states on this path are opaque. To show that  $G_{\rho} \in \llbracket P \rrbracket$ , the key is to *reuse* these states and identify a *similar* transition path that generates each thread of  $G_{\rho}$  from the initial state. By Definition 4, it means we have to show that for each thread t in  $G_{\rho}$ , there exists a state  $st'_m$  such that  $st'_m.G = G_{\rho}|_t$  and  $st'_0 \to_t^* st'_m$  with  $st'_0.sprog = P(t)$ . Note that  $st'_m$  is not necessarily a terminal state.

We first borrow the notion of *data-abstract equivalence* from [8] and lift it to execution graphs.

DEFINITION 8 (DATA-ABSTRACT EQUIVALENT GRAPH). A plain execution graph G is data-abstract equivalent to another plain execution graph G' if there is a map  $\delta: G.\mathsf{Evt} \to G'.\mathsf{Evt}$  such that for each event  $e \in G.\mathsf{Evt} = \langle tid, eid, typ, val, loc \rangle$ , there is  $\delta(e) \in G'.\mathsf{Evt} = \langle tid, eid, typ, val', loc \rangle$  for some val'. In addition, for each  $\langle e_1, e_2 \rangle \in G.\mathsf{po}$ ,  $\langle \delta(e_1), \delta(e_2) \rangle \in G'.\mathsf{po}$  and vice versa.

We write  $G \approx G'$  if G is data-abstract equivalent to G.

The data-abstract equivalence relation can be extended naturally to the map  $\Psi$  and the set ctrl in a state. Now we use this notion to define a similarity relation over states. Let  $st, st' \in S$  tate where  $st = \langle sprog, pc, \Phi, G, \Psi, ctrl, \theta, \Phi^{\theta} \rangle$  and  $st' = \langle sprog', pc', \Phi', G', \Psi', ctrl', \theta', \Phi^{\theta'} \rangle$ . We say  $st' \approx st$ , if sprog = sprog', pc = pc',  $G \approx G'$ ,  $\Psi \approx \Psi'$ ,  $ctrl \approx ctrl'$ ,  $\theta \approx \theta'$ , and  $\Phi^{\theta} = \Phi^{\theta'}$ . For each read event  $r \in G$ .Rd,  $\theta(r) = \theta(\delta(r))$ . Essentially, two states are data-abstract equivalent if they only differ by the concrete values on each read events. It's easy to see that if two states are identical, then they are data-abstract equivalent, i.e.,  $st = st' \Rightarrow st \approx st'$ .

As illustrated in Fig. 6, for each thread t, if we can construct a similar state transition path  $st'_0 \to \ldots \to st'_n$  that generates  $G_\rho|_t$  from an empty state containing the same source program as P(t), then by Definition 4 we can conclude that  $G_\rho \in [P]$ .

We can use the following lemma to prove that an execution graph is executable.

LEMMA 1. Let  $G_{\rho}$ ,  $G_{\sigma}$  be well-formed execution graphs and  $G_{\sigma} \in \llbracket P \rrbracket$ . If for each thread  $t \in G_{\rho}$ . Thrd,  $t \in G_{\sigma}$ . Thrd and there is a  $\sqsubseteq$ -ordered set  $\{st'_{0}, \ldots, st'_{m}\}$  such that for  $i \in 0 \ldots m$ ,

• each state  $st'_i$  satisfies the invariant  $subst(\Phi^{\theta}(r), val^{\theta}(\Psi(r))) = \Phi(r)$  for  $r \in \text{Reg}$ ,

$$st_0 \longrightarrow st_1 \longrightarrow \ldots \longrightarrow st_m \longrightarrow \ldots \longrightarrow st_k$$

$t_0' \longrightarrow st_1' \longrightarrow \ldots \longrightarrow st_m'$

Fig. 6. Similar State Transitions

- for each  $st'_i$  there exists a state  $st_i \in Path(G_{\sigma}|_t)$  with  $st_i \approx st'_i$  and  $st_0 = st'_0$ ,

- for each  $st'_i$  if  $st'_i.sprog(st'_i.pc) = if expr goto k then <math>st_i.\Phi(expr) = st'_i.\Phi(expr)$ ,

- $st'_m.G = G_\rho|_t$ ,

then  $G_{\rho} \in [P]$ .

Lemma 1 uses the notion of *states* to reason about the relation between the input execution and the witness execution. In addition, it requires each event in the witness graph to be concrete. The following lemma simplifies the requirements of executability, focusing the reasoning process on *events* and allowing events with symbolic values.

Lemma 2. Let  $\hat{G}_{\rho}$  be a well-formed symbolic plain execution graph and  $G_{\sigma}$  be a concrete input execution graph such that  $G_{\sigma} \in [\![P]\!]$ . If  $\hat{G}_{\rho}$  satisfies the following conditions:

- there is a map  $\delta: \hat{G_\rho}$ . Evt  $\to G_\sigma$ . Evt such that for each event  $e \in \hat{G_\rho}$ . Evt,  $\delta(e) \approx e$  and if  $e.val \in Val$  (i.e., e.val is concrete), then  $\delta(e) = e$ .

- if  $\langle e_1, e_2 \rangle \in G_{\sigma}$ .po and  $e_2 = \delta(e_2')$  for some  $e_2' \in \hat{G}_{\rho}$ . Evt, then there is an event  $e_1' \in \hat{G}_{\rho}$ . Evt such that  $e_1 = \delta(e_1')$  and  $\langle e_1', e_2' \rangle \in \hat{G}_{\rho}$ . po,

- for each thread  $t \in \hat{G}_{\rho}$ . Thrd and each event  $e \in \hat{G}_{\rho}|_{t}$ . Evt, if there is a read event  $r \in \hat{G}_{\rho}|_{t}$ . Rd, such that  $\langle \delta(r), \delta(e) \rangle \in G_{\sigma}$ . ctrl, then  $r.val \in Val$  (i.e., r.val is concrete),

- for each write event  $w \in \hat{G}_{\rho}$ . Wrt, if  $w.val \in Val$  (i.e., w.val is concrete), then for all  $r \in \hat{G}_{\rho}$ . Rd such that  $\langle \delta(r), \delta(w) \rangle \in G_{\sigma}$ . data,  $r.val \in Val$  (i.e., r.val is concrete). then  $\hat{G}_{\rho} \in \llbracket P \rrbracket$ .

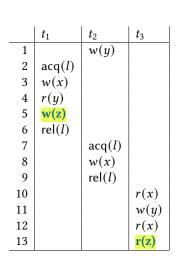

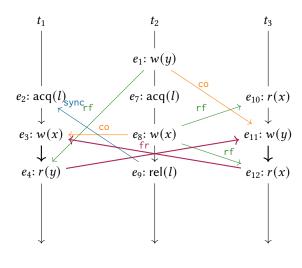

Example. We use an example to demonstrate the intuition behind LEMMA 2.

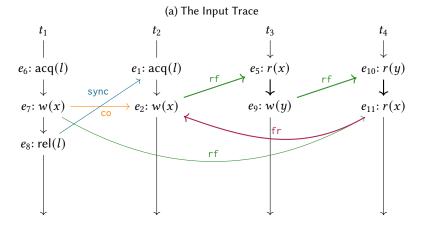

Fig. 7 shows three execution graphs. In particular,  $G_{\sigma}$  in Fig. 7a is a concrete execution graph,  $\hat{G_{\rho 1}}$  in Fig. 7b is a symbolic execution graph with  $e_2'$  and  $e_4'$  having symbolic values, and  $\hat{G_{\rho 2}}$  in Fig. 7c is a symbolic execution graph with  $e_7''$  having a symbolic value. For better readability, we annotate events in  $\hat{G_{\rho 1}}$  with single primes and events in  $\hat{G_{\rho 2}}$  with double primes. Assuming  $G_{\sigma} \in \llbracket P \rrbracket$ , it's easy to check that we can apply Lemma 2 to show that  $\hat{G_{\rho 1}} \in \llbracket P \rrbracket$  and  $\hat{G_{\rho 2}} \in \llbracket P \rrbracket$ . Indeed, the map  $\delta_1 = \{e_i' \mapsto e_i\}$  for  $i \in 2 \dots 4$  satisfies the requirements of Lemma 2, which shows  $\hat{G_{\rho 1}}$  is executable, and the map  $\delta_2 = \{e_i'' \mapsto e_i\}$  for  $i \in 1 \dots 7$  satisfies the requirements of Lemma 2, which shows  $\hat{G_{\rho 2}}$  is executable. Note that both  $\hat{G_{\rho 1}}$  and  $\hat{G_{\rho 2}}$  are plain symbolic execution graphs, which means they do not inherit memory orders from  $G_{\sigma}$  other than a subset of po. Intuitively, the requirements in Lemma 2 are the minimal conditions that ensure the control and data flows included in  $\hat{G_{\rho 1}}$  and  $\hat{G_{\rho 2}}$  are the same as in  $G_{\sigma}$ .

Specifically,  $\hat{G}_{\rho 1}$  is a symbolic execution graph with two symbolic events. The value of  $e_4'$  is a symbolic value  $\hat{b}$ , since the concrete value of  $e_4$  is not critical to the control flow included in  $\hat{G}_{\rho 1}$ . On the other hand, there is a control dependency from  $e_3$  to  $e_4$  in  $G_{\sigma}$ . In order for a write event accessing y to occur, regardless its value, the concrete value of  $e_3$  must be preserved. Therefore, in

$$e_{1} \colon w(z) = 1 \xrightarrow{\text{rf}} e_{2} \colon r(z) = 1 \qquad e_{5} \colon w(x) = 1$$

$$\downarrow \text{po} \qquad \downarrow \text{po}$$

$$\downarrow \text{ctrl} \qquad \downarrow \text{ctrl}$$

$$e_{4} \colon w(y) = 1 \qquad e_{7} \colon r(z) = 1$$

(a) A Concrete Execution Graph  $G_{\sigma}$

$$e_{2}': r(z) = \hat{a} \quad e_{5}': w(x) = 1$$

$$\downarrow \qquad \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$e_{3}': r(x) = 1$$

$$\downarrow \qquad \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$e_{3}'': r(x) = 1 \quad e_{6}'': r(y) = 1$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$e_{4}': w(y) = \hat{b} \qquad \qquad \qquad e_{4}'': w(y) = 1 \quad e_{7}'': r(z) = \hat{c}$$

- (b) A Symbolic Execution Graph  $\hat{G_{\rho 1}}$

- (c) A Symbolic Execution Graph  $\hat{G_{

ho 2}}$

Fig. 7. An example of using Lemma 2 to show executability of symbolic execution graphs

$\hat{G}_{\rho 1}$ ,  $e_3'$  stays as a concrete event with the same value as  $e_3$ . Note that in order to be well-formed, each read event with a concrete value must be justified by a concrete write event accessing the same location with the same value. From  $G_{\sigma}$ , we can see that  $e_5$  justifies the value of  $e_3$ . Therefore, the corresponding event  $e_5'$  also has the same concrete value. Although there is a data dependency from  $e_2$  to  $e_4$ , since  $e_4'$  now becomes a symbolic event,  $e_2'$  does not need to preserve the concrete value of  $e_2$ . Hence,  $e_2'$  with a symbolic value  $\hat{a}$  does not impact the executability of  $\hat{G}_{\rho 1}$ .

On the other hand,  $\hat{G}_{\rho 2}$  includes more events than  $\hat{G}_{\rho 1}$ , which leads to more restrictions on the values of the events.  $e_7''$  is a symbolic event for the same reason as  $e_4'$  being symbolic. There is a control dependency from  $e_6$  to  $e_7$ . Hence  $e_6$ 's value must be preserved to make sure the control flow is not altered. From  $G_{\sigma}$ , we can see that  $e_4$  justifies the value of  $e_6$ . Hence, the corresponding event in  $\hat{G}_{\rho 2}$ ,  $e_4''$ , must have the same concrete value as  $e_4$ . Now  $e_2''$  must have the same concrete value as  $e_2$  as well, since there is a data dependency from  $e_2$  to  $e_4$  and  $e_4$ 's value is preserved. Again, to justify the concrete values of  $e_2''$  and  $e_3''$ ,  $e_1''$  and  $e_5''$  are also included as concrete events. As a result, only  $e_7''$  is a symbolic event and all other events included in  $\hat{G}_{\rho 2}$  have to preserve their original values from  $G_{\sigma}$  to ensure executability.

#### 4.4 Memory Consistency

The second major component of soundness is memory consistency. Most existing work in predictive analysis focuses on sequentially consistent executions (except for [9], which focused on TSO and PSO models). Under sequential consistency, an execution can be treated as a linear sequence of events, i.e., a *trace*. However, under relaxed memory models, executions may not be linearizable by a global order. Instead, the validity of an execution is determined by a *memory consistency model*, which can be represented as a pair of constraints: emptiness and irreflexivity constraints over event orders [12].

To keep the presentation manageable, we consider Multicopy-Atomic (MCA) models. It remains our future work to integrate the semantics of lock operations into non-MCA models. Under an MCA model, if a write event is visible to a thread that is not its issuing thread, then it is visible to all other threads as well. This property simplifies the axiomatic model because all cross-thread communications can be treated as global in MCA models. The rest of the section relies on MCA models that are defined in the following way.

An execution is consistent under an MCA memory model if

irreflexive  $(ppo \cup com)^+$

irreflexive  $(po-loc \cup com)^+$

where the ppo stands for *preserved program order*. Each MCA model provides its own definition of ppo. The second requirement corresponds to *SC-per-location*.

In addition, we omit treatment of Read-Modify-Write (RMW) events, and consider only fully fenced lock events. All of these could be accommodated without impacting the logic of our approach. Under sequential consistency (SC), preserved program order is given by all po orders.

$$ppo = po$$

Under x86-TSO [20], preserved program order is given by

$$ppo = po \cap ((Wrt \times Wrt) \cup (Rd \times Wrt) \cup (Rd \times Rd))$$

Under ARMv8, preserved program order is given by the *locally-ordered-before* (lob) order from [1].

We now augment these memory models with lock operations. We first define a new relation sync order. For each lock l, there is a linear order among the critical sections protected by l. For each two ordered critical sections of the same lock  $CS_1$  and  $CS_2$ , where  $CS_1 \rightarrow CS_2$ , sync $_l$  is a relation from the release event of  $CS_1$  to the acquire event of  $CS_2$ . sync is the union of sync $_l$  for all locks  $l \in Lock$ .

We do not allow events to move into or out of a critical section. Therefore, each lock operation also has a fence-like effect. In practice, this is typically given by the use of fence instructions inside lock implementations. We augment preserved program order with the program orders where a lock operation occurs in-between. We use L to denote the union of lock acquires and releases.

The most important property that locks should provide is mutual exclusion. Given two critical sections protected by the same lock, the events in one critical section should be all finished before the events in another critical section start. In other words, there should not be any interleaving among the events from two critical sections.

We can rule out this behavior by augmenting MCA models with:

irreflexive (ppo

$$\cup$$

(po; [L])  $\cup$  ([L]; po)  $\cup$  com  $\cup$  sync)<sup>+</sup>

It's easy to see that moving events into a critical section while preserving all other program orders does not introduce new behavior as it only monotonically adds more ppo order into the execution graph.

Finally, there may be open critical sections in an execution graph. By well-formedness of an execution graph, there is at most one open critical section per lock. The open critical sections should always be ordered as the last critical section in the linear order of that lock. Therefore, we add one more restriction to the memory model. For each lock l, if there is an open critical section, let acq(l) be the acquire event of that open critical section. The for every release event rel(l) of the same lock occur in the same execution, we have  $\langle rel(l), acq(l) \rangle \in sync$ .

Overall, we have the following definition for an MCA memory model augmented with lock operations.

Definition 9 ( $\mathcal{M}$ -consistency). Given a definition of preserved program order ppo from an memory model  $\mathcal{M}$  for an MCA architecture, a complete execution graph  $G_{\rho}$  is  $\mathcal{M}$ -consistent if

- $(po-loc \cup com)^+$  is irreflexive, and

- $(ppo \cup (po; [L]) \cup ([L]; po) \cup com \cup sync)^+$  is irreflexive, and

- for each lock  $l \in Lock$ , if  $G_{\rho}.Open(l) = acq(l)$ , then for each release event  $rel(l) \in G_{\rho}.Rel$ ,  $\langle rel(l), acq(l) \rangle \in G_{\rho}.sync$ .

As a sanity check, we prove a property that is a weaker variation of the DRF-SC theorem. The following proposition states that, if every pair of conflicting access is protected by some lock, which means there is no data race in the program, then the program is guaranteed to be sequentially consistent.

PROPOSITION 3. Let P be a program. For each sequentially consistent execution graph of P, if for each conflicting memory event  $e_1 \bowtie e_2$ ,  $e_1, e_2 \in CS_l$  for some  $l \in Lock$ , then every sound execution of P is sequentially consistent.

Given the definition of soundness, in the rest of this paper, we explain how one can prove that a given predictive analysis is sound.

### 5 A Recipe to Prove Soundness

The soundness definition from §4 has an existential quantifier over witness execution graphs. Hence, a proof of soundness for a given predictive analysis should provide a scheme to construct a witness execution graph for each reported concurrent bug and show that the witness satisfies each of the four requirements of soundness.

Note that the soundness definition asks for a complete execution graph where the value of each event is concrete. In some cases where the rf order of the witness execution is altered from that of the input execution, the values of some events are not computable without knowing the program source code. On the other hand, there is a subset of events whose values are critical for the execution control flow, and therefore have to be preserved. For events that do not affect the control flow, their concrete values are unimportant to the soundness of the algorithm. Therefore, we use a *symbolic* execution graph as an intermediate form, which allows the values of a subset of events to be symbolic if they do not need to be preserved before memory orders are inserted.

To prove soundness for a predictive analysis, a witness execution can be constructed in the following steps:

- §5.1 **Constructing a Symbolic Plain Execution.** Construct a symbolic plain execution graph  $\hat{G}_{\rho}$  with an event map  $\delta:\hat{G}_{\rho}$ . Evt  $\rightarrow G_{\sigma}$ . Evt, such that  $\hat{G}_{\rho} \triangleright b$ , and  $\hat{G}_{\rho}$  is well-formed and executable.

- §5.2 **Inserting Consistent Memory Orders.** Insert rf, co, and sync memory orders so that  $\hat{G}_{\rho}$  is  $\mathcal{M}$ -consistent up to concrete events and well-formed.

- §5.3 **Mapping to a Concrete Execution.** Map the symbolic execution  $\hat{G}_{\rho}$  to a concrete execution graph  $G_{\rho}$  with a complete rf-map while preserving all the properties.

In the rest of this section, we discuss each step in details. The proofs of the propositions and lemmas can be found in Appendix  $\mathbb D$ .

# 5.1 Constructing a Symbolic Plain Execution

Recall that a symbolic plain execution graph  $\hat{G}_{\rho}$  is a tuple (Evt, po) where some of the events have symbolic values. To ensure executability, the program order po from  $G_{\sigma}$  has to be preserved in  $\hat{G}_{\rho}$ .

Therefore, the task of constructing  $\hat{G}_{\rho}$  is essentially finding a set of events to be included in  $\hat{G}_{\rho}$ . Evt and determine the concrete values of a subset of events in the set.

The set of events Evt to be included in the witness execution is determined by dependencies and lock semantics. We identify two types of dependencies, *control* and *data* dependencies. While modern architectures define other types of dependencies as well, control and data dependencies are two most fundamental dependencies that determines the soundness of a predictive analysis in the language of this paper.

- **Control dependencies**. Control dependencies determine the control flow of the program. Formally, it is a subset of po whose domain is a set of read events. For each  $\langle r, e \rangle \in \texttt{ctrl}$  in an execution, the value of r determines whether the instruction that generates e is eventually executed at some point. In each execution state, the field ctrl is a set of read events that is used to compute control dependency.

- **Data dependencies**. Data dependencies determine the data flow of the program. Formally, it is a subset of po whose domain is a set of read events and whose range is a set of write events. For each  $\langle r, w \rangle \in$  data in an execution, the value of r determines the value of w.

The two dependencies encapsulate the sequential and control properties from any memory model considered in this paper. They are sufficient to determine a set of events in the input execution that each bug sequence depends on. As hinted from the reasoning process in the example of Fig. 7, we can use the two dependencies to find two sets of events, a set of events to be mapped to the events in the witness execution graph and a set of events of which the values need to be preserved. In other words, there is a set of events  $S_{\sigma} \subseteq G_{\sigma}$ . Evt with a subset  $C_{\sigma} \subseteq S_{\sigma}$  such that the existence of events in  $S_{\sigma}$  and the values of the events in  $C_{\sigma}$  determine the control flow of the execution that leads to the bug sequence. These events can then be used to construct a plain execution graph, i.e. the witness execution. To ensure the witness execution satisfy the first three soundness requirements,  $S_{\sigma}$  and  $C_{\sigma}$  have to satisfy the following properties.

DEFINITION 10. Let  $\langle S_{\sigma}, C_{\sigma} \rangle$  be two event sets such that  $C_{\sigma} \subseteq S_{\sigma} \subseteq G_{\sigma}$ . Evt. We say  $\langle S_{\sigma}, C_{\sigma} \rangle$  enables a bug sequence b if

```

I. For each event e \in b, if \langle e', e \rangle \in G_{\sigma}.po, then e' \in S_{\sigma}

```

II.  $S_{\sigma}$  is downward-closed w.r.t.  $G_{\sigma}$ .po

III.  $S_{\sigma}$  is lock-feasible (Definition 7)

IV. For each event  $e \in b$ , if  $\langle r, e \rangle \in G_{\sigma}$ .ctrl, then  $r \in C_{\sigma}$

V. For each  $e \in S_{\sigma}$ , if  $\langle r, e \rangle \in G_{\sigma}$ .ctrl, then  $r \in C_{\sigma}$

VI. For each  $e \in C_{\sigma}$ , if  $\langle r, e \rangle \in G_{\sigma}$ .data, then  $r \in C_{\sigma}$

VII. For each  $r \in C_{\sigma}$ , there exists a write  $w \in C_{\sigma}$  such that r.val = w.val and r.loc = w.loc VIII.  $S_{\sigma} \cap b = \emptyset$

In the examples in Fig. 7, if  $b = e_4$ , then  $S_{\sigma} = \{e_2, e_3, e_5\}$  and  $C_{\sigma} = \{e_3, e_5\} \subseteq S_{\sigma}$ ; if  $b = e_7$ , then  $S_{\sigma} = \{e_1, e_2, e_3, e_4, e_5, e_6\}$  and  $C_{\sigma} = S_{\sigma} = \{e_1, e_2, e_3, e_4, e_5, e_6\}$ .

Given such a pair of event sets  $\langle S_{\sigma}, C_{\sigma} \rangle$ , one can construct a plain execution graph  $\hat{G}_{\rho} = (\text{Evt}, \text{po})$  by the following steps. Let  $S_{\rho}$  be an event set such that  $S_{\rho} \approx S_{\sigma}$  and  $C_{\sigma} \subseteq S_{\rho}$ . In other words, there is a bijective event map  $\delta : S_{\rho}$ . Evt  $\to S_{\sigma}$ . Evt where  $\delta(e) \approx e$  for each  $e \in S_{\rho}$  and  $\delta(e) = e$  for each  $e \in C_{\sigma}$ . Then we set the following components of  $\hat{G}_{\rho}$ :

```

\begin{split} & \cdot \ \hat{G}_{\rho}.\mathsf{Evt} = S_{\rho}. \\ & \cdot \ \hat{G}_{\rho}.\mathsf{po} = \delta^{-1}(G_{\sigma}.\mathsf{po} \cap (\delta(\hat{G}_{\rho}.\mathsf{Evt} \times \hat{G}_{\rho}.\mathsf{Evt}))). \end{split}

```

In the examples in Fig. 7, the constructed graph is  $\hat{G}_{\rho 1} \setminus \{e'_4\}$  if  $b = e_4$ ; the constructed execution graph is  $\hat{G}_{\rho 2} \setminus \{e''_1\}$  if  $b = e_7$ .

Given a pair of event set  $\langle S_{\sigma}, C_{\sigma} \rangle$  that enables the bug sequence b, the constructed witness plain execution  $\hat{G}_{\rho}$  can be shown to satisfy the first three soundness requirements.

Proposition 4. If  $\langle S_{\sigma}, C_{\sigma} \rangle$  enables a bug sequence b, then  $\hat{G}_{\rho}$  is well-formed up to concrete events and  $\hat{G}_{\rho} \rhd b$ .

Proposition 5. If  $\langle S_{\sigma}, C_{\sigma} \rangle$  enables a bug sequence b, and  $G_{\sigma} \in [\![P]\!]$ , then  $\hat{G}_{\rho} \in [\![P]\!]$ .

Since the soundness of the witness execution depends on the pair  $\langle S_{\sigma}, C_{\sigma} \rangle$ , one essentially has to provide such a pair and show that it enables the reported bug sequence.

In practice, the precise information of control and data dependencies are rarely known to the predictive analysis. In addition, if the analysis does not record the concrete values of events in the input execution, then it'd be hard to determine which write event has the same value of a read event, as required by one of the conditions above. One way to overcome these challenges is tracing the po  $\cup$  rf orders of the input execution  $G_{\sigma}$  and leverage the well-formed properties that they provide. The following lemma shows that any plain execution graphs of which the event set is downward-closed with respect to po and a subset of rf is read-feasible and executable.

Lemma 3. Let  $\hat{G}_{\rho} = (\text{Evt}, \text{po})$  be a plain execution graph such that  $\hat{G}_{\rho}$ . Evt is downward-closed with respect to  $G_{\sigma}$ . (po  $\cup$  rf| $_{C}$ ) where C is the set of concrete read and write events of  $\hat{G}_{\rho}$  such that  $((\text{data} \cup \text{rf})^*; \text{ctrl})^+ \subseteq C$  for a bug sequence b, and  $\delta(e) = e$  for each  $e \in C$ . Then  $\hat{G}_{\rho}$  is read-feasible up to C and executable.

Lemma 3 does not guarantee lock feasibility. Lock feasibility may be ensured by tracing a partial order from  $G_{\sigma}$ , as stated in the following lemma.

Lемма 4. Let  $\hat{G}_{\rho}$  = (Evt, po) be a plain execution graph such that  $\hat{G}_{\rho}$ . Evt is downward-closed with respect to  $G_{\sigma}$ . (po ∪ sync), then  $\hat{G}_{\rho}$  is lock-feasible.

As we will see in §6, analyses that over-approximate the control and data dependencies can apply Lemma 3 and Lemma 4 to show the well-formedness and the executability requirements.

## 5.2 Inserting Consistent Memory Orders

After a symbolic plain execution graph is determined, the next step is providing a memory order insertion scheme so that the complete execution graph is memory consistent. The goal in this step is to obtain an  $\mathcal{M}$ -consistent symbolic graph such that rf-map is defined and well-formed for all concrete read events, co is a total order among all write events to the same location, and sync is well-formed for each lock. While the insertion scheme is, in general, specific to the predictive algorithm, in some cases memory orders of  $G_{\sigma}$  can be reused since it is sequentially consistent, which automatically ensures  $\mathcal{M}$ -consistency.

We begin by inserting rf orders among concrete events in  $\hat{G}_{\rho}$ . For each concrete read in  $\hat{G}_{\rho}$ , by Lemma 2, we know that its value is inherited from the correspondent event in  $G_{\sigma}$ . From (VII) of Definition 10, there is a write event whose value is also preserved. Therefore, we can insert the same rf order between the preserved write and preserved reads.

Moreover, note that the only case where a cycle would potentially occur is when critical sections are reordered, due to the second requirement for  $\mathcal{M}$ -consistency: open critical sections should be ordered after all other critical sections of the same lock. Hence, if any of the events occur in the bug sequence is in an open critical section, all other critical sections of the same lock in  $\hat{G_\rho}$  have to be ordered before the open critical section. For critical sections that originally occurred after some

events from the bug sequence, it means they would need to be reordered with the bug events in  $\hat{G}_{\rho}$ . In order to show that  $\hat{G}_{\rho}$  is  $\mathcal{M}$ -consistent, one has to show that such reordering can never cause a cycle that is forbidden by  $\mathcal{M}$  to occur.

On the other hand, if the set of events in  $\hat{G}_{\rho}$  is guaranteed *not* to include such critical sections, then the memory orders from  $G_{\sigma}$  can be reused and the resulting execution graph is still sequentially consistent. The following lemma demonstrates this idea.

Lemma 5. Let  $G_{\sigma}$  be an input execution such that  $G_{\sigma}$  is sequentially consistent, equipped with a linear trace order. Let  $\hat{G}_{\rho}$  be a symbolic plain execution that is well-formed, and  $\hat{G}_{\rho} \rhd b$  where b is a reported bug. If for all acquire event  $\operatorname{acq}(l) \in \hat{G}_{\rho}$ . Evt such that  $l \in \operatorname{LocksHeld}(e)$ ,  $\langle \operatorname{acq}(l), e \rangle \in G_{\sigma}$ . trace for each event  $e \in b$ . Evt that is in a critical section where the acquire event of the critical section  $\operatorname{acq}(l) \in \hat{G}_{\rho}$ , then there exists a memory order insertion scheme over  $\hat{G}_{\rho}$ . Evt such that  $\hat{G}_{\rho}$  is sequentially consistent.

As we will see in §6, predictive analyses that preserve synchronization orders [18, 19] use this lemma to insert memory orders when constructing the witness execution.

# 5.3 Mapping to a Concrete Execution

Finally, once the memory orders are inserted while maintaining  $\mathcal{M}$ -consistency, the following lemma shows that there exists a well-formed concrete graph, i.e.,  $G_{\rho}$ , that can be obtained by concretizing the symbolic events in  $\hat{G}_{\rho}$  and all properties from the previous steps are preserved.

Lemma 6. Let  $\hat{G}_{\rho}$  be a symbolic execution with a well-formed rf-map over concrete events, a total co order over write events to the same location, and a well-formed sync over lock events. If  $\hat{G}_{\rho}$  is  $\mathcal{M}$ -consistent and  $\hat{G}_{\rho} \in \llbracket P \rrbracket$  with  $e.val \in \mathsf{Val}$  for each  $e \in \mathsf{preserve}(b)$ , then there exists a map  $\Theta : \mathsf{Sym} \to \mathsf{Val}$  such that the concrete execution  $G_{\rho} = \Theta(\hat{G}_{\rho})$  with a complete rf-map is  $\mathcal{M}$ -consistent and  $G_{\rho} \in \llbracket P \rrbracket$ .

The result of applying this lemma is a complete and concrete execution graph that satisfies the four requirements of soundness, which finishes the soundness proof.

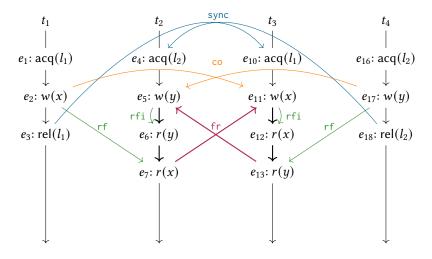

# 6 Proving Race Prediction Algorithms Sound

In §2, we reviewed a set of existing predictive analyses that used various soundness definitions as their correctness criteria. Fig. 8 shows six of the nine analyses from §2 that focus on predicting data races with their race reporting criteria. Because the soundness definitions used in their papers were different, their soundness proofs are hard to compare with each other. In this section, we take a closer look at these algorithms and use our recipe on each of them to show their soundness. The point of this section is to showcase a unified and structured way of proving soundness of existing algorithms.

In the rest of the section, we assume  $e_1, e_2 \in G_\sigma$  are two events from the input execution and  $e_1 \bowtie e_2$ . In addition, to keep the discussions concise,  $\langle e_1, e_2 \rangle \in G_\sigma$ .trace.

#### 6.1 M2

M2 [21] determines data races by computing linearizable closures. In particular, a set of events,  $\mathsf{RCone}_\sigma(e_1, e_2)$ , is first computed. Then a partial order is inserted among the events in this set until a linearizable state is reached. If  $e_1$  or  $e_2$  is included in  $\mathsf{RCone}_\sigma(e_1, e_2)$ , or a cycle occurs during the process of inserting the partial order, then  $\langle e_1, e_2 \rangle$  is not a data race. Otherwise,  $\langle e_1, e_2 \rangle$  is reported as a data race. Formally,  $\mathsf{RCone}_\sigma(e_1, e_2)$  is defined inductively as the following:

|      | Analysis         | Race Reporting Criterion                                                                                                          |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| [21] | M2               | P is a strict partial order over $RCone_\sigma(e_1,e_2)$                                                                          |

| [8]  | RVPredict        | $\exists \rho \models \Phi^{\sigma}_{mhb} \land \Phi^{\sigma}_{lock} \land \Phi^{\sigma}_{race}(e_1, e_2)$                        |

| [9]  | MCR-TSO          | $\exists \rho \models \Phi^{\sigma}_{\text{ppo}} \land \Phi^{\sigma}_{\text{lock}} \land \Phi^{\sigma}_{\text{race}}(e_1, e_2)$   |

| [5]  | НВ               | the first $e_1 \parallel_{hb} e_2$                                                                                                |

| [18] | SHB              | $e_1 \parallel_{shb} e_2$                                                                                                         |

| [19] | SyncP            | $\{e_1, e_2\} \cap SPIdeal_{\sigma}(e_1, e_2) = \emptyset$                                                                        |

| §F   | Enhanced-MCR-tso | $\exists \rho \models \Phi^{\sigma}_{ppo} \land \Phi^{\sigma}_{lock} \land \Phi^{\sigma}_{race}(e_1, e_2)$ after Read Elimination |

Fig. 8. Race Reporting Criterion of Various Race Prediction Algorithms

- $\{\operatorname{prev}_{\sigma}(e_1), \operatorname{prev}_{\sigma}(e_2)\} \subseteq \operatorname{RCone}_{\sigma}(e_1, e_2), \text{ where } \langle \operatorname{prev}_{\sigma}(e), e \rangle \in G_{\sigma}.\operatorname{po}|_{imm} \text{ for all } e \in G_{\sigma}.\operatorname{Evt},$

- for each event  $e \in G_{\sigma}$ . Evt, if  $\langle e, e' \rangle \in G_{\sigma}$ . (po  $\cup \ rf$ ) for some event  $e' \in \mathsf{RCone}_{\sigma}(e_1, e_2)$ , then  $e \in \mathsf{RCone}_{\sigma}(e_1, e_2)$ ,

- for each acquire event  $acq(l) \in RCone_{\sigma}(e_1, e_2)$ , if  $acq(l).tid \neq e_1.tid$  and  $acq(l).tid \neq e_2.tid$ , then there is a release event  $rel(l) \in RCone_{\sigma}(e_1, e_2)$  such that match(rel(l)) = acq(l).

Then a closure algorithm is applied over events in  $\mathsf{RCone}_{\sigma}(e_1, e_2)$ . The algorithm inserts a strict partial order  $\mathsf{P}$  based on the following closure rules.

- 1.  $G_{\sigma}$ .(po  $\cup$  rf) $|_{\mathsf{RCone}} \subseteq \mathsf{P}$ ,

- 2. For every  $\operatorname{acq}(l) = \operatorname{Open}_l(\mathsf{RCone}_\sigma(e_1, e_2))$  and every  $\operatorname{rel}(l) \in \mathsf{RCone}_\sigma(e_1, e_2).\mathsf{Rel}$ ,  $\operatorname{rel}(l) \xrightarrow{\ \ } \operatorname{acq}(l)$ ,

- 3. If  $w' \xrightarrow{P} r$  and  $w \xrightarrow{rf} r$  then  $w' \xrightarrow{P} w$  for each  $w, w' \in \mathsf{RCone}_{\sigma}(e_1, e_2)$ . Wrt and  $r \in \mathsf{RCone}_{\sigma}(e_1, e_2)$ . Rd where w'.loc = w.loc = r.loc

- 4. If  $w \xrightarrow{p} w'$  and  $w \xrightarrow{rf} r$  then  $r \xrightarrow{p} w'$  for each  $w, w' \in \mathsf{RCone}_{\sigma}(e_1, e_2)$ . Wrt and  $r \in \mathsf{RCone}_{\sigma}(e_1, e_2)$ . Rd where w'.loc = w.loc = r.loc

- 5. For  $\operatorname{acq}_1(l) = \operatorname{match}(\operatorname{rel}_1(l))$ ,  $\operatorname{acq}_2(l) = \operatorname{match}(\operatorname{rel}_2(l))$ , if  $\operatorname{acq}_1(l) \xrightarrow{\mathbb{P}} \operatorname{rel}_2(l)$ , then  $\operatorname{rel}_1(l) \xrightarrow{\mathbb{P}} \operatorname{acq}_2(l)$

Moreover, if there exists any pair of events  $e \bowtie e' \in \mathsf{RCone}_{\sigma}(e_1, e_2)$  such that  $e_i.tid \notin \{e.tid, e'.tid\}$  for a non-deterministically chosen  $i \in \{1, 2\}$ ,  $e \xrightarrow{\mathsf{trace}} e'$ , and  $e \parallel_{\mathsf{P}} e'$ , then  $\langle e, e' \rangle$  is added into  $\mathsf{P}$  and the closure rules above are applied to reach a fixed point.

The soundness of M2 is stated as the following.