# Automatic Hardware Pragma Insertion in High-Level Synthesis: A Non-Linear Programming Approach

STÉPHANE POUGET, University of California, Los Angeles LOUIS-NOËL POUCHET, Colorado State University JASON CONG, University of California, Los Angeles

High-Level Synthesis enables the rapid prototyping of hardware accelerators, by combining a high-level description of the functional behavior of a kernel with a set of micro-architecture optimizations as inputs. Such optimizations can be described by inserting pragmas for e.g. pipelining and replication of units, or even higher level transformations for HLS such as automatic data caching using the AMD/Xilinx Merlin compiler. Selecting the best combination of pragmas, even within a restricted set, remains particularly challenging and the typical state-of-practice uses design-space exploration to navigate this space. But due to the highly irregular performance distribution of pragma configurations, typical DSE approaches are either extremely time consuming, or operating on a severely restricted search space.

In this work we propose a framework to automatically insert HLS pragmas in regular loop-based programs, supporting pipelining, unit replication (coarse- and fine-grain), and data caching. We develop an analytical performance and resource model as a function of the input program properties and pragmas inserted, using non-linear constraints and objectives. We prove this model provides a lower bound on the actual performance after HLS. We then encode this model as a Non-Linear Program, by making the pragma configuration unknowns of the system, which is computed optimally by solving this NLP. This approach can also be used during DSE, to quickly prune points with a (possibly partial) pragma configuration, driven by lower bounds on achievable latency. We extensively evaluate our end-to-end, fully implemented system, showing it can effectively manipulate spaces of billions of designs in seconds to minutes for the kernels evaluated.

Additional Key Words and Phrases: HLS, FPGA, Non-Linear Programming, Program Optimization

#### **ACM Reference Format:**

# **1 INTRODUCTION**

High-level synthesis (HLS) [8, 51] compilers [16, 25, 33, 44] and source-to-source compiler for HLS [15, 18, 20, 43, 46, 47] can reduce development time while delivering a good performance for the designs. However, achieving a satisfactory Quality of Results (QoR) often requires design-space exploration (DSE). This is because the design space, including which pragmas to insert and where, can not only contain millions of points, but typically does not present characteristics suitable for fast analytical exploration, such as convexity and regularity. Although the existing DSE methods [34, 38, 42] can find designs with a good QoR, it comes at a high computation cost: for example, hundreds of designs may be concretely instantiated using HLS to compute its estimated QoR during exploration [38].

Our main objective in this work is to provide a system to automatically insert a set of hardware pragmas for HLS, that delivers a good QoR and yet significantly reduces the search time needed to obtain the final design. To address this challenge, we propose NLP-DSE , a framework built on top of the AMD/Xilinx Merlin source-to-source compiler [43]. This framework automatically inserts pragmas for unrolling/parallelization, pipelining, tiling and data caching *for affine programs* [19], prior to HLS. These Merlin pragmas can also be inserted using a DSE approach, such as AutoDSE [38] or

<sup>2024.</sup> Manuscript submitted to ACM

HARP [35], which we use as reference for our evaluations. However, in contrast to AutoDSE [38] and HARP [35], we specifically restrict the class of programs we manipulate to affine programs that are regular loop-based computations. In turn, it enables us to develop a hybrid analytical approach to drive the search, combined with a lightweight DSE to reduce the number of designs actually explored. NLP-DSE preserves, and often even improves, the final QoR of designs produced.

To this end, we create a novel Non-Linear Programming approach to automatically insert pragmas in an existing program. We develop an analytical model combining latency and resources, targeting regular loop-based kernels [27], that is parameterized by the pragma configuration. We can then designate the pragma configuration as the unknowns of this model, solving it by NLP to obtain the set of pragmas that minimizes latency. An important design principle of our approach is to ensure that the latency computed *is a lower bound on the achievable latency for a given pragma configuration.* This enables efficient pruning during DSE: any design predicted to have a latency lower bound higher than the best latency obtained through exploration so far is necessarily slower and does not need exploration. To overcome the fact that optimizing compilers, and the overall HLS toolchain underneath, may not apply optimizations as expected (e.g., due to insufficient resources, or limitations of the compiler's implementation), we develop a lightweight NLP-based DSE approach, exploring parts of the design space with different types and amounts of hardware parallelism and array partitioning factors. We make the following contributions:

- We present an analytical performance and resource model specifically built for AMD/Xilinx Vitis and Merlin compilers, which is amenable to optimization via non-linear programming.

- We prove our model is a lower bound on the final latency of the design, under reasonable hypothesis. This enables fast pruning of the design space: it ensures designs which have a higher latency lower bound than the best design found so far can be safely pruned from the search.

- We develop an NLP-based DSE approach exploiting this model, targeting regular loop-based kernels, which can significantly outperform DSE-based search approaches such as AutoDSE, delivering equal or better QoR in a significantly less search time.

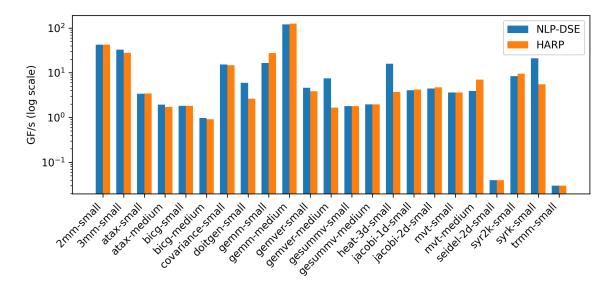

- We implement NLP-DSE it as an end-to-end, fully automated system and use it to conduct extensive evaluation on 47 benchmarks including kernels from linear algebra, image processing, physics simulation, graph analytics, datamining, etc. [27]. Our results show the ability of our approach to find in most cases a better QoR than AutoDSE, in significantly less time. Furthermore, in most instances, our approach outperforms HARP in terms of QoR within a comparable timeframe.

The paper is organized as follows. Section 2 motivates our approach and solution proposed. Section 3 presents our analytical performance and resource model. Section 4 delves into proving it is a lower bound on the final QoR. In Section 5, we introduce a non-linear formulation based on this model to automatically find pragma configurations by NLP optimization. Section 6 presents our lightweight DSE approach. Finally, sections 7 and 10 are devoted to evaluating our method validating the effectiveness of our approach and presenting related work, before concluding.

# 2 BACKGROUND AND MOTIVATION

, ,

#### 2.1 Pragma-based Optimizations for HLS

This work targets the automatic optimization of FPGA designs using HLS [8, 51], in particular when using compilers to automatically generate HLS-friendly optimized programs such as the AMD/Xilinx Merlin Compiler [6, 7, 43]. Falcon

Computing Solutions developed this source-to-source automation tool for FPGAs, which was acquired by Xilinx in late 2020 and is now open source.

HLS has made FPGA usage more accessible, and many projects are looking to further democratize this field by automating optimizations [13, 15, 18, 38, 46]. Merlin was developed to improve the performance, reduce the development time of HLS-based designs and simplify the search space. To achieve this goal, it automatically generates data transfers between off-chip and on-chip memory and inserts important Vitis pragmas, such as for array partitioning. Moreover, Merlin does specific code transformation for the targeting hardware in adequacy with the hardware directive describe by the user. Additionally, it enables parallel coarse-grained processing elements by encapsulating inner loops as functions.

Merlin includes hardware directive pragmas such as:

- ACCEL parallel <factor=x>, which creates x parallel instances, and Merlin restructures the code accordingly if the loop nest has more than x iterations. This pragma can be used for fine-grained and coarse-grained parallelization. Merlin will insert the array partitioning corresponding to the parallelization and optimize memory coalescing accordingly for the memory transfer;

- ACCEL pipeline <II=y> for pipelining;

- ACCEL tile <factor=z> for strip-mining a loop by z, enabling Merlin to insert other pragmas such as data caching in a loop with smaller trip count, matching the on-chip resources available and reducing off-chip communications;

- ACCEL cache <array=a> which transfers all required elements of array *a* from off-chip to on-chip to perform computations within the specified sub-region. If the user does not specify this pragma, it can be applied automatically by Merlin.

In this work we target the automatic generation of pragmas for the Merlin toolchain, to enable the seamless deployment of optimizations such as array partitioning, off-chip data transfers using bursts, coarse-grain and fine-grain replication, etc. These pragma-directed optimizations are implemented by Merlin on loop-based programs, combining source code transformations and the automatic insertion of Vitis pragmas to drive the HLS process.

We note our approach is not restricted to Merlin, nor a particular version of a toolchain: by adjusting the parameters of the performance model, such as operation latency, resource usage per operation(s), etc. one can easily target other toolchains than the one we evaluate here.

## 2.2 DSE for Pragma Insertion

Design-space exploration techniques typically trade-off coverage for speed [38, 56]. That is, it may impose restrictions on the input programs supported, on the pragmas/transformations considered, etc. in order to accelerate the search [28, 56]. To overcome the difficulty of providing accurate performance models for arbitrary programs, HLS may be invoked to obtain a QoR estimate, without imposing any restriction on the input programs and transformations used. However HLS time for highly optimized designs combining various Merlin pragmas (e.g., parallelism and caching) can quickly reach several hours per design, making the search process particularly time-consuming. One may restrict the space of pragmas considered, and especially their parameter range, to reduce search time. General-purpose DSE approaches such as AutoDSE [38] are by design agnostic to the input program features and search space explored, preserving generality. But as we demonstrate in this paper, it also misses opportunities for search acceleration that can be provided by careful static analysis, leading to missed performance opportunities.

In this work, we target the *specialization* of the DSE process to *affine programs*, that are programs with a statically analyzable control-flow and dataflow. By restricting the class of programs supported to affine programs, we can deploy *exact* loop and data dependence analysis [12]. More importantly, as shown in Section 5, for this class of programs we can model accurately enough the behavior of a design in terms of latency and resource usage by using *non-linear programming*, significantly accelerating the DSE time for such programs by avoiding the need for actual HLS estimation in numerous cases.

We illustrate the performance merits and limitations of such general-purpose DSE [38] on three important loop-based linear algebra benchmarks. *GEMM*, the classical dense general matrix-multiply, and *2mm* shown in Listing 1 which computes the product of three matrices D = alpha \* A \* B \* C + beta \* D. Both are key computations in e.g., inference of transformers [9]. *Gramschmidt* computes QR decomposition using the Gram-Schmidt process. In later Section 7 we evaluate these benchmarks using various problem sizes, ranging from kBs to MBs of footprints for the matrices to demonstrate the robustness of our approach to varying and large problem sizes. Below we use matrices of about 300kB each.

```

Loop0: for (i1 = 0; i1 < 180; i1++)

Loop1: for (j1 = 0; j1 < 190; j1++) {

S0: tmp[i1][j1] = 0.0;

Loop2: for (k1 = 0; k1 < 210; ++k1)

S1: tmp[i1][j1] += alpha * A[i1][k1] * B[k1][j1];

}

6

Loop3: for (i2 = 0; i2 < 180; i2++)

Loop4: for (j2 = 0; j2 < 220; j2++) {

8

S2: D[i2][j2] *= beta;

Loop5: for (k2 = 0; k2 < 190; ++k2)

S3: D[i2][j2] += tmp[i2][k2] * C[k2][j2];

12

}

13 }

```

,,

Listing 1. 2mm code:  $D = \alpha \times A \times B \times C + \beta \times D$

The search spaces considered here quickly reach billions of feasible designs, even for kernels containing only a handful of loops and statements. Considering *2mm*, each loop can have a pragma tile and parallel, all with factors that are divisors of the loop trip count and a pragma pipeline. We obtain a space of  $1.37 \times 10^{10}$  valid designs. This represents 432 years if assuming one design takes a single second to evaluate. Obviously, only a minimal fraction of these spaces is actually explored, making it essential to adequately select the order in which designs are explored.

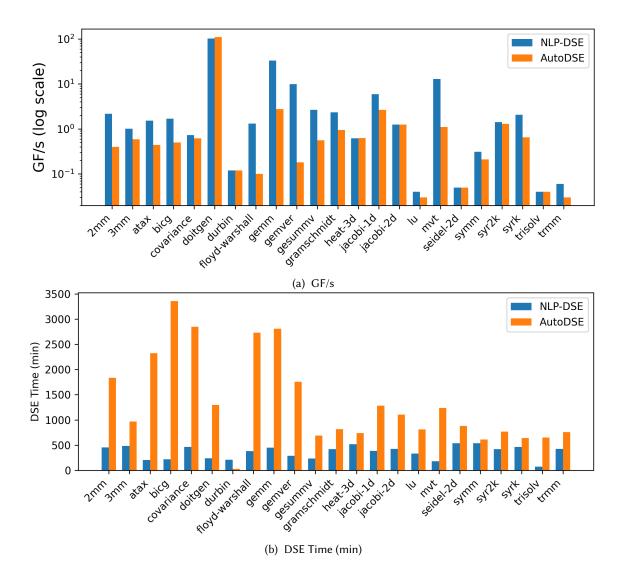

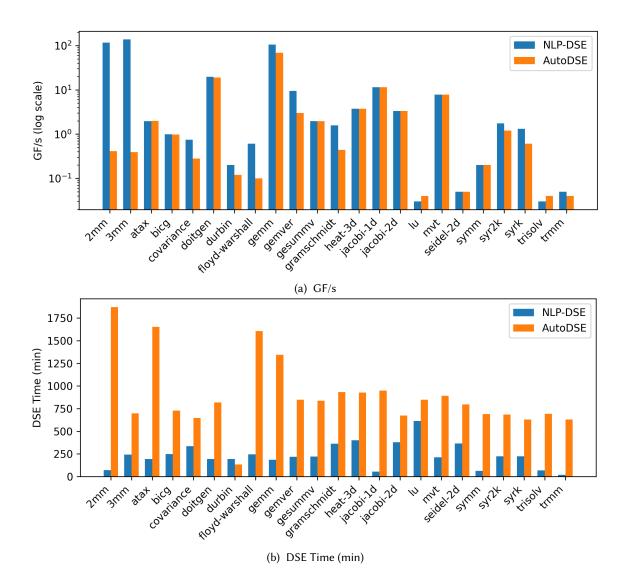

Table 1 displays the performance (in GigaFlop/s, GF/s) of the original programs, from PolyBench/C [27], when fed to Merlin as-is. The best design found by AutoDSE, given a time budget of 20 hours per benchmark and a timeout of 3 hours per HLS run, is also reported. AutoDSE uses a bottleneck-driven search approach, which targets the improvement of the code section with the lowest throughput [38]. It unambiguously achieves particularly solid improvements over a naive design without pragmas. However, we show in Table 3 below that a carefully built DSE technique, exploiting the regularity of affine programs and leveraging non-linear programming, can provide order(s) of magnitude higher performance for these exact benchmarks, all while using significantly less search time.

Automatic Hardware Pragma Insertion in High-Level Synthesis: A Non-Linear Programming Approach

|             | 2mm (footprint: 773kB) |            | Gemm (f | ootprint: 579kB) | Gramsch. (footprint: 15MB) |            |  |

|-------------|------------------------|------------|---------|------------------|----------------------------|------------|--|

|             | GF/s                   | Time (min) | GF/s    | Time (min)       | GF/s                       | Time (min) |  |

| Original    | 0.10                   | N/A        | 0.07    | N/A              | 0.14                       | N/A        |  |

| AutoDSE     | 0.41                   | 1,870      | 68.91   | 1,345            | 0.95                       | 819        |  |

| Improvement | 4.1x                   |            | 984x    |                  | 6.8x                       |            |  |

Table 1. Comparison of throughput (GF/s) between the AutoDSE framework and the source-to-source compiler Merlin without pragma insertion for the kernels 2mm, Gemm and Gramschmidt

# 2.3 Limitations of General-Purpose DSE

By analyzing the space explored by the DSE for these three examples, valuable hints can be observed which drive the design of NLP-DSE .

Exploration of the space. AutoDSE [38] utilizes the HLS compilers as a black box, in order to select the configurations that minimize the objective function. The tools are agnostic of the input program shape and if AutoDSE detects that Merlin did not apply the pragmas as expected it allows the DSE to prune the design after Merlin has generated the HLS-C code. These frameworks use incremental DSEs, i.e., having no information on the characteristics of the program, they explore the space by increasing the parallelism in order to respond to a problem, e.g., a bottleneck for Auto-DSE.

Table 2 shows the number of valid designs in each space and the number of synthesized, pruned, timeout designs for each kernel. As we can see with a timeout of 20 hours for the DSE and a timeout of 3 hours for each synthesis, the DSE only allows a tiny part of the space to be explored.

|                                  | 2mm                   | Gemm                 | Gramsch.             |

|----------------------------------|-----------------------|----------------------|----------------------|

| Nb. valid designs (Space)        | $1.37 \times 10^{10}$ | $2.30 \times 10^{6}$ | $1.22 \times 10^{8}$ |

| Nb. design Synthetized (AutoDSE) | 15                    | 25                   | 15                   |

| Nb. design pruned (AutoDSE)      | 49                    | 34                   | 239                  |

| Nb. design timeout (AutoDSE)     | 37                    | 27                   | 11                   |

| Nb. Design explored (AutoDSE)    | 101                   | 86                   | 265                  |

Table 2. Investigation into the design space and exploration extent concerning synthesized designs, pruned designs, and designs reaching timeout by the AutoDSE framework for the kernels 2mm, Gemm, and Gramschmidt.

Over Parallelization. AutoDSE is an incremental method: in order to speed up the search AutoDSE will seek to pipeline certain loops which leads to an unrolling of the innermost loops. Without knowledge of the code, trip counts and resources used this leads to over-use of parallelism, leading to timeouts and/or over-use of resources. For 2mm, it attempts to pipeline the outermost loops, leading to the above issues.

Parallelism imbalance. Botlleneck analysis will make it possible to select which part of the code to optimize as a priority [38]. However, this priority does not take into account parallelism (i.e., hardware resources) that shall be deployed for other parts of the code. This creates code with regions that are extremely/fully parallelized, and others without any parallelism.

For 2mm, the fastest design found by AutoDSE mainly optimizes one loop body. When AutoDSE tries to optimize the second loop body, it favors the unroll factors to the power of two for the innermost loop and goes directly to the outermost loop. This does not improve performance or create configurations which are pruned. The fact that it does not try the other unrolls factors for the innermost loop before optimizing the other pragmas creates a loss of performance. For Gemm and Gramschmidt, the DSE finds designs with a good QoR. However the DSE wastes much time exploring too large unroll factors, which generates ponderously long synthesis times without giving any result as the HLS timeout is reached. The time spent increasing the unroll factor for certain pragmas without result does not allow the unroll factor of other pragmas to be increased, which results in missed performance.

#### 2.4 Overview of NLP-DSE

, ,

NLP-DSE targets the (conservative) modeling of the performance and resources used by a design, such that arbitrary pragma configurations from Section 2.1 are applied on a regular, loop-based affine program. It deploys accurate static analysis to reason on the input program features, and a complex non-linear analytical performance model to drive the design space exploration. That is, *NLP-DSE is a method for automatic pragma insertion that is specialized to affine programs*. As demonstrated below, this specialization enables significantly better QoR and DSE time for affine programs than general-purpose DSE approaches such as AutoDSE.

To make our approach feasible and maintain sufficient accuracy in analytical models, we focus on programs with static control flow that can be exactly captured using *polyhedral structures* [12]. These affine, or polyhedral, programs can be analyzed to obtain the exact information about loop trip counts and dependencies, enabling more accurate performance predictors [56]. The Affine MLIR dialect specializes in modeling such programs [19, 46].

Although NLP-DSE it can be used to compute pragmas without any DSE, the inherent limit of analytical models persist with NLP-DSE : as the implementation details of the back-end toolchain for HLS and synthesis may not be accurately captured by a model, DSE remains needed for best performance.

NLP-DSE enables the exploration of different parallelism and configuration spaces by constraining the level of parallelism, as detailed in Section 6. Our model is presented in Sec. 3, and we prove it is a performance lower bound in Sec. 4, an important feature to be able to prune designs during the search without the risk of losing performance. The associated NLP formulation is provided in Section 5.

|                  | 2mm    |           |         | Gemm   |           |         |      |           |         |

|------------------|--------|-----------|---------|--------|-----------|---------|------|-----------|---------|

|                  | GF/s   | Time (mn) | DSP (%) | GF/s   | Time (mn) | DSP (%) | GF/s | Time (mn) | DSP (%) |

| Original         | 0.10   | N/A       | 0       | 0.07   | N/A       | 0       | 0.14 | N/A       | 0       |

| AutoDSE          | 0.41   | 1,870     | 14      | 68.91  | 1,345     | 10      | 0.95 | 819       | 1       |

| NLP-DSE -FS      | 13.19  | N/A       | 24      | 105.18 | N/A       | 26      | 2.34 | N/A       | 2       |

| NLP-DSE          | 117.48 | 70        | 39      | 105.18 | 185       | 26      | 2.34 | 420       | 2       |

| Imp. vs. AutoDSE | 286x   | 26x       |         | 1.5x   | 7.2x      |         | 2.4x | 1.9x      |         |

The effectiveness of our framework is demonstrated in Table 3, comparing the performance and time-to-solution of NLP-DSE . We also display the result of the first synthesizable design produced, NLP-DSE -FS.

Table 3. Comparison of NLP-DSE , NLP-DSE -FS, which provides the result of the first synthesizable design, the source-to-source compiler Merlin without pragma insertion, and AutoDSE in terms of throughput (GF/s), DSE time (mn) and DSP utilization (%) for the kernels 2mm, Gemm, and Gramschmidt.

For *Gemm* and *Gramsch* the first design synthetizable has the best QoR of our DSE. For these two kernels, NLP-DSE implements better parallelism usage compared to AutoDSE. Specifically, our methodology successfully identified configurations with more balanced levels of parallelism. In contrast, AutoDSE failed to achieve the same level of parallelization within the fixed time for the DSE. On one hand, AutoDSE tends to explore first configurations with low levels of parallelism. On the other hand, it concurrently explores design spaces with excessively high levels of parallelism, leading to timeouts and unmet resource constraints. This discrepancy highlights the merits of seeding the DSE with configurations optimized for maximum parallelism, and systematically adjusts this level based on hardware directives and compiler expectations, as implemented in NLP-DSE.

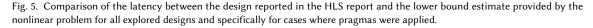

For *2mm*, the first design synthetizable allows us to have a better QoR vs. AutoDSE but our DSE shows its interest in finding a configuration 8.9 times faster than the first configuration found by the DSE. More detail can be found in Section 8.

It is noteworthy that our Design Space Exploration (DSE) approach, detailed in Section 6, deviates intentionally from AutoDSE. Unlike AutoDSE, which starts with a pragma-free configuration and gradually introduces pragmas, we begin with configurations characterized by the lowest theoretical latency, emphasizing high levels of parallelism. This deliberate departure from the conventional approach is further discussed in Section 6.

In Section 7, we present a comprehensive evaluation of our framework, demonstrating the improvements over AutoDSE that can be achieved by specializing to affine programs, in terms of design throughput and time-to-solutions across various benchmarks. The results indicate an average performance improvement of 5.69x and 17.24x in terms of DSE time and design throughput, respectively, with only a marginal decrease in throughput for 1 out of 47 benchmarks. Importantly, the time-to-solution of NLP-DSE it is consistently up to 30x faster than AutoDSE across all benchmarks.

# 3 MODELING PROGRAMS AND THEIR PRAGMAS

We now present our analytical performance model. We assume the input programs are polyhedral programs [12, 14], and therefore exact loop trip counts can be computed by static analysis, similarly for all data dependencies.

## 3.1 Program Representation

We represent programs using a summary of their Abstract syntax tree (AST), with sufficient information to estimate latency and resource consumption by analytical modeling. Intuitively, we can build a constructor-style description of the summary AST, and then directly instantiate the complete formula for estimating e.g., latency, based on loop properties. We first introduce this representation before proving how to compute a latency lower bound with it.

We employ the code below as a running example with the pragma above the loops as AMD/Xilinx Merlin. For presentation simplicity, we assume each loop iterator in the program region has been renamed to a unique name, so that we can uniquely identify loops in the code by their iterator name.

The summary AST for this loop is simply built by creating one node per for loop and one per statement Sx, the body of a loop is made of loops and/or statements, and their nodes are children of said loop in the tree, listed in their

syntactic order. For example, above, utilizing a constructor notation, it gives:  $Loop_i(Loop_{j1}(S1), Loop_{j2}(S2, S3))$ . Then, a simple rewrites of this tree using loop properties and composition operators will lead to the proposed analytical model, as outlined below. We first describe the loop properties we associate to each loop. We consider combinations of the following pragmas, based on Merlin's optimizations, for the loop with iterator i:

- #pragma ACCEL parallel <factor=ufi>

- #pragma ACCEL pipeline <II=IIi>

- #pragma ACCEL tile

,,

• #pragma ACCEL cache <variable=a>

We therefore associate to each loop i in the program a property vector that informs about the optimizations to be considered. We define  $\vec{P}V_i$  as follows:  $\vec{P}V_i :< ispipelined_i$ ,  $II_i$ ,  $uf_i$ ,  $tile_i$ ,  $TC_i^{min}$ ,  $TC_i^{max} >$  where we have:  $ispipelined_i = 1$  if the loop is pipelined, 0 otherwise;  $II_i$  is the initiation interval, set to 1 by default;  $uf_i$  is the parallelism/unroll factor, set to 1 by default (no #pragma ACCEL parallel pragma) and set to  $TC_i^{max}$  if parallel is defined without a factor  $uf_i$  specified.  $tile_i$  is the TC of the innermost loop after strip mining.  $TC_i^{min}$  is the minimal trip count of loop i, for any of its execution in the program. We also compute the maximal trip count over all executions. These values are computed using polyhedral analysis on the loops [29]. The pragma cache transfers above the loop i the data needed for the computation of this loop nest for the array a.

This vector is built by syntactic analysis on the program, where the default value  $PV_i :< 0, 1, 1, 1, TC_i^{min}, TC_i^{max} >$  is used for a loop without any pragma. Once all loops have been annotated by their  $\vec{P}V$  properties, subsequent treatment can be implemented to mirror the optimizations implemented by the back-end tool.

*Modeling Vitis optimizations.* AMD/Xilinx Vitis will apply several optimizations automatically, such as auto-pipeline and auto-loop-flatten, some other optimizations when the user gives a compilation option such as tree reduction.

Only a loop with a constant TC, i.e.,  $TC_{max} = TC_{min}$  can be unrolled. The unroll pragma options allow to specify the unrolling factor,  $uf_i$ . When the factor is not specified, it implies that the factor is equal to the TC of the loop. When a loop is pipelined, all innermost loops are automatically fully unrolled. Hence, we also propagate unrolling information, e.g., to mark a full loop nest for full unrolling if an outer loop is marked with #pragma ACCEL pipeline. The pipeline pragma options allow to specify the objective II the user wants to achieve. When II is not specified, it is automatically set to 1. In addition, Vitis will auto-pipeline with a target II of 1 the innermost loops which are not fully unrolled for each nested loop.

Within Vitis, users can enable optimizations like logarithmic time reduction through tree reduction. This optimization choice will be a global option within our model, applicable across the entire model rather than being limited to a specific loop.

*Modeling Merlin optimizations.* Finally, Merlin will also add automatic optimizations. It will explicitly strip-mine a loop when it is partially unrolled with the innermost loop having a *TC* equal to the factor and the unrolled pragma applied to that loop. Similarly to Vitis, Merlin will auto-pipeline. Merlin also applies a program transformation for certain pragmas. When there are two perfectly nested and partially unrolled loops, Merlin swaps the two loops strip-mined (if legal), unrolled innermost and flatten and pipeline the two outermost loops. Further, Merlin will automatically transfer the data from off-chip to on-chip and cache on-chip with packing, with a maximum packing of 512 bits for our FPGA while computing if the footprint of the data fit on-chip by static analysis. The pragma tile allows Merlin to strip mine a loop and give the compiler the opportunity to transfer less/more data while respecting resource constraints. For our

model we suppose an optimistic data transfer i.e., all memory transfers are done with a packing of 512 bits and each data are transferred once (perfect data reuse).

Consequently, the set of possible  $\vec{PV}_l$  vectors are adjusted by analyzing the input code, and modifying their initial value, possibly further constraining the set of possible  $\vec{PV}_l$  based on which program transformation will be performed, as described above. Overall, the  $\vec{PV}_l$  vectors, along with the summarized AST, contain sufficient information to capture several source-to-source transformations performed by the Merlin compiler for coarse- and fine-grain parallelization, and reason on the likeliness of the optimization to succeed at HLS time (e.g., capturing loops with non-constant trip count).

# 4 MODELING OF LATENCY AND RESOURCE LOWER BOUND

We present the foundational components of our analytical performance model and demonstrate how this model computes a lower bound on latency while adhering to resource constraints. The theorems and their accompanying proofs can be found in Appendix B.

# 4.1 Analytical Model Template

Consider the expression  $I_i^{\vec{P}V_i}(X)$  for the loop *i*, where *X* denotes a subpart of the program, and the operators are defined as follows:

$$I_{i}^{\vec{PV}_{i}}(X) = \begin{cases} \left| II_{i} \cdot \left( \frac{TC_{i}^{aog}}{uf_{i}} - \operatorname{ispip}_{i} \right) \right| + X & \text{if loop } i \text{ is pipelined} \\ & (\operatorname{ispip}_{i} = 1) \\ \\ \left| II_{i} \cdot \left( \frac{TC_{i}^{aog}}{uf_{i}} - \operatorname{ispip}_{i} \right) \right| \cdot X & \text{otherwise } (\operatorname{ispip}_{i} = 0) \end{cases}$$

For simplicity, we will represent the operation as  $\odot$  to differentiate between the two different cases. Let  $C_i^{\vec{P}V_i}(X_1, X_2, \dots, X_n)$  which compose the different sub part of a program under the loop *i*.

$$C_i^{\vec{P}V_i}(X_1, X_2, \dots, X_n) = \begin{cases} \max(X_1, X_2, \dots, X_n) & \text{if } (X_1, \dots, X_n) \text{ do not have dependencies (WaR, RaW, WaW)} \\ \sum_{k=1}^n X_k & \text{otherwise} \end{cases}$$

1 S0: x1 += y;

1 S0: x1 += y;

2 S1: x2 += x1 + z;

2 S1: x2 += z;

Listing 2. Example of code where two statements have

dependencies

case inparallel = 1.

Listing 3. Example of code where two statements do not have dependency

In List 2, statements S0 and S1 exhibit dependencies, resulting in a program latency equal to the sum of their latencies, corresponding to *issequence* = 1. Conversely, the statements in List 3 lack dependencies, allowing S0 and S1 to be executed concurrently. Therefore, the latency is determined by the maximum of S0 and S1 latencies, representing the

9

Finally,  $SL_i^{\tilde{P}V_i}(\vec{S}_k)$  denotes a region of straight-line code (e.g., an inner-loop body). Intuitively, SL will represent a lower bound on the latency of a code block such that by composition across all loops as per the template formula, the result remains a lower bound on the full program latency.

Given the summary AST of the program in constructor form, and the set of  $\vec{P}V_i$  vectors for each loop, we build the analytical formula template as follows:

- (1) replace the  $Loop_i(\vec{X})$  operator by  $I_i^{\vec{P}V_i}(\vec{X})$  operator;

- (2) replace the  $\vec{X}$  list by  $C_i^{\vec{P}V_i}(\vec{X})$ ;

- (3) replace statement lists inside loop i  $\vec{S}_x$  by  $SL_i^{\vec{P}V_i}(\vec{S}_x)$ .

For our example, we can rewrite the expression:

$$Loop_i(Loop_{j1}(S1), Loop_{j2}(S2, S3))$$

as

, ,

$$I_{i}^{\vec{P}V_{i}}(C^{\vec{P}V_{i}}(I_{j_{1}}^{\vec{P}V_{j_{1}}}(SL_{j_{1}}^{\vec{P}V_{j_{1}}}(S1)), I_{j_{2}}^{\vec{P}V_{j_{2}}}(SL_{j_{2}}^{\vec{P}V_{j_{2}}}(S2, S3))))$$

Upon substituting the definitions and assuming that the statements are independent, we obtain:

$$\left[II_{i} \cdot \left(\frac{TC_{i}^{aog}}{uf_{i}} - \operatorname{ispip}_{i}\right)\right] \odot \max\left(\left[II_{j1} \cdot \left(\frac{TC_{j1}^{aog}}{uf_{j1}} - \operatorname{ispip}_{j1}\right)\right] \odot SL_{j1}^{\vec{P}V_{j1}}(S1), \left[II_{j2} \cdot \left(\frac{TC_{j2}^{aog}}{uf_{j2}} - \operatorname{ispip}_{j2}\right)\right] \odot SL_{j2}^{\vec{P}V_{j2}}(S2, S3)\right)$$

#### 4.2 A Formal Model for Latency

Our objective is to formulate a lower bound on the latency of a program after HLS. We therefore have put several restrictions: we assume the input program is a polyhedral program, that is the control-flow is statically analyzable; all loops can be recognized and their trip count computed; and all array / memory accesses can be exactly modeled at compile-time. No conditional can occur in the program. While our approach may generalize beyond this class, we limit here to these strict assumptions.

To maintain a lower bound on latency by composition, we operate on a representation of (parts of the) program which is both schedule-independent and storage-independent: indeed, a lower bound on this representation is necessarily valid under any schedule and storage eventually implemented. *We however require HLS to not change the count and type of operations*. Furthermore, for lower bounding purposes, we assume unless stated otherwise  $\forall i$ , *inparallel*<sub>i</sub> = 1. We will discuss in the next section a more realistic but compiler-dependent approach to set *inparallel*<sub>i</sub>, based on dependence analysis.

We assume programs are made of affine loops, that are loops with statically computable control-flow, with loop bounds made only of intersection of affine expressions of surrounding loop iterators and program constants. We now assume loop bodies (i.e., statements surrounded by loops) have been translated to a list of statements, with at most a single operation (e.g., +, -, /, \*) per statement. Operations are n-ary, that is they take  $n \ge 0$  input scalar values as operand, and produce 0 or 1 output scalar value. A memory location can be loaded from (resp. stored to) an address stored in a scalar variable. This is often referred to as straight-line code . This normalization of the loop body facilitates the computation of live-in/live-out data for the code block, and the extraction of the computation graph. Note the region can be represented in Static Single Assignment form, to ensure different storage location for every assignment, facilitating the construction of the operation graph. In addition we require the input program to not contain useless operations which may be removed by the HLS toolchain e.g. by dead code elimination, as illustrated in Listing 4.

, ,

```

1 int example(int y, int z){

2     int x;

3     S0: x = 12 + y; // dead-code elimination

4     S1: x = y + z;

5     return x;

6 }

```

Listing 4. Example of Code Illustrating Dead Code Elimination: As Statement S1 writes to variable x, but the value of x assigned in Statement S0 is never used, the compiler will remove Statement S0.

The restriction can be summarized as:

- The input program is a pure polyhedral program [14], and its analysis (loop trip counts for every loop, all data dependences [12]) is exact.

- No HLS optimization shall change the number of operations in the computation: strength reduction, common sub-expression elimination, etc. shall either first be performed in the input program before analysis, or not be performed by the HLS toolchain. The program also does not contain "useless" operations that may be removed by the compiler.

- We only model DSP and BRAM resources for the considered kernel, ignoring all other resources. We do not

model LUT and FF resources, because from experience in the loop-based benchmarks we consider DSP and

BRAM resources are the most constraining resources. Moreover, the estimation of LUTs and FFs is more tedious.

- We assume resource (DSP) sharing across different operations executing at the same cycle is not possible.

An important term is *SL*, a latency lower bound for a region of straight-line code. To maintain a lower bound on latency by composition, we operate on a representation of (parts of the) program which is both schedule-independent and storage-independent: the operation graph, or CDAG [11]. Indeed, a lower bound on this representation is necessarily valid under any schedule and storage eventually implemented and can be used to prove I/O lower bounds on programs [11] which is the directed acyclic graph with one node per operation in the code region, connecting all producer and consumer operations to build the operation graph. Then, we can easily compute the length of its critical path, which represents the minimal set of operations to execute serially.

We can compute the directed acyclic graph made of all statements (i.e., all n-ary operations), connecting all producer and consumer operations, to build the operation graph:

Definition 4.1 (Operation Graph). Given a straight-line code region R made of a list L of statements  $S \in L$ , the operation graph OG is the directed graph  $\langle N, V_I, root, V_O \rangle, E \rangle$  such that  $\forall S_i \in L$ ,  $N_{S_i} \in N$ ; and for every operation with output o and inputs  $\vec{i}$  in  $L \forall S_i, \forall i_k \in \vec{i}_{S_i}, e_{i_k,o} \in E, \forall S_i : (o_{S_i}, \vec{i}_{S_i}) \in L, S_j : (o_{S_j}, \vec{i}_{S_j}) \in L$  with  $S_i \neq S_j$  then we have  $E_{S_i,S_j} \in E$  iff  $o_{S_i} \cap \vec{i}_{S_j} \neq \emptyset$ . For every input (resp. output) in  $S_i$  which is not matched with an output (resp. input) of another  $S_j$  in L, create a node  $V_{val} \in V_I$  (resp.  $V_O$ ) for this input (resp. output) value. If  $dim(\vec{i}_{S_i}) = 0$  then an edge  $e_{root,S_i}$  is added to E.

From this representation, we can easily define key properties to subsequently estimate the latency and area of this code region, such as its span, or critical path.

Definition 4.2 (Operation Graph critical path). Given  $OG^L$  an operation graph for region L. Its critical path  $OG_{cp}$  is the longest of all the shortest paths between every pairs  $(v_i, v_o) \in \{V_I, root\}, V_O >$ . Its length is noted  $\#OG_{cp}^L$ .

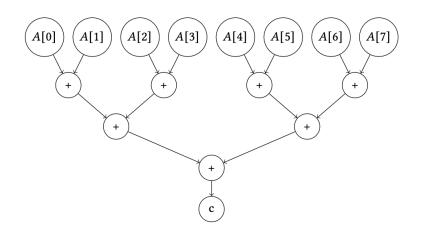

On the graph on the Figure 1 the critical paths from A[i] to  $c, \forall i \in [[0, 7]]$ , have the same length.

4.2.1 Latency Lower Bound. We can build a simple a lower bound on the latency of an operation graph:

THEOREM 4.3 (LOWER BOUND ON LATENCY OF AN OPERATION GRAPH). Given infinite resources, and assuming no operation nor memory movement can take less than one cycle to complete, the latency  $LAT_{cp}^{L} \ge \#OG_{cp}^{L}$  is a lower bound on the minimal feasible latency to execute L.

We can then build a tighter lower bound on the number of cycles a region L may take to execute, under fixed resources, by simply taking the maximum between the weighted span and the work to execute normalized by the resources available.

THEOREM 4.4 (LATENCY LOWER BOUND UNDER OPERATION RESOURCE CONSTRAINTS). Given  $R_{op}$  a count of available resources of type op, for each operation type, and LO(op) the latency function for operation op, with  $LO(op) \ge 1$ . #L(op)denotes the number of operations of type op in L. We define  $LO(#OG_{cp}^L) = \sum_{n \in cp} LO(n)$  the critical path weighted by latency of its operations. The minimal latency of a region L is bounded by

$$Lat_{R_{op}}^{L} \ge \max(LO(\#OG_{cp}^{L}), \max_{o \in op}(\lceil \#L(o) \times LO(o)/R_{o} \rceil))$$

This theorem provides the building block to our analysis: if reasoning on a straight-line code region, without any loop, then building the operation graph for this region and reasoning on its critical path is sufficient to provide a latency lower bound.

```

1 #pragma ACCEL unroll factor=uf

2 L0: for (i = 0; i < N; i++)

3 S0: s[i] = 0;

4 #pragma ACCEL pipeline

5 L1: for (i = 0; i < M; i++) {

6 S1: q[i] = 0;

7 #pragma ACCEL unroll

8 L2: for (j = 0; j < N; j++) {

9 S2: s[j]+=r[i]*A[i][j];

10 S3: q[i]+=A[i][j]*p[j];

11 }

12 }

12 }</pre>

```

, ,

Listing 5. Bicg code:  $s = r \times A$ ;  $q = A \times p$

For example, in Lst. 5, if we consider the sub-loop body composed of loops L2 (fully unrolled) and the statements S2 and S3 as straight-line code regions, we can calculate the critical paths for S2 and S3 as follows: For S2, the critical path is given by:  $cp_{S2} = \max(L(+) + L(*), N \times (DSP_+ + DSP_*)/R_o)$  with  $DSP_o$  the number of DSP for the operation o. For S3, the critical path is determined by:  $cp_{S3} = \max(L(+) \times \log(N) + L(*), N \times (DSP_+ + DSP_*)/R_o)$ , considering the possibility of a tree reduction. In this context, the critical path for the entire sub-loop body is the maximum of these two individual critical paths, expressed as  $\max(cp_{S2}, cp_{S3})$ .

We now need to integrate loops and enable the composition of latency bounds.

4.2.2 Loop Unrolling: partial unroll. Loop unrolling is an HLS optimization that aims to execute multiple iterations of a loop in parallel. Intuitively, for an unroll factor  $UF \ge 1$ , UF replications of the loop body will be instantiated. If  $TC_l$  mod  $UF_l \ne 0$  then an epilogue code to execute the remaining  $TC_l \mod UF_l$  iterations is needed.

Unrolling can be viewed as a two-step transformation: first strip-mine the loop by the unroll factor, then consider the inner loop obtained to be fully-unrolled. The latency of the resulting sub-program is determined by how the outer-loop generated will be implemented. We assume without additional explicit information this unrolled loop will execute in a non-pipelined, non-parallel fashion. Note this bound requires to build the operation graph for the whole loop body. This is straightforward for inner loops and/or fully unrolled loop nests, but impractical if the loop body contains other loops. We therefore define a weaker, but more practical, bound *that enables composition*:

THEOREM 4.5 (MINIMAL LATENCY OF A PARTIALLY UNROLLED LOOP WITH FACTOR UF). Given a loop l with trip count  $TC_l$  and loop body L, and unroll factor  $UF \leq TC$ . Given available resources  $R_{op}$  and latencies  $L(op) \geq 1$ . Given L' the loop body obtained by replicating UF times the original loop body L. Then the minimal latency of l if executed in a non-pipelined fashion is bounded by:

$$Lat_{R_{op}}^{l,S} \ge \lfloor TC/UF \rfloor \times Lat_{R_{op}}^{L'}$$

```

1 #pragma ACCEL parallel UF=4

2 L1: for (i = 0; i < 8; i++) {

3 S0: a[i] = b[i] * c[i];

4 }</pre>

```

```

Listing 6. Example before partial unrolling

```

```

1 // explicitly unroll with UF=4

2 L1: for (i = 0; i < 8; i+=4) {

3 S0: a[i] = b[i] * c[i];

4 S1: a[i+1] = b[i+1] * c[i+1];

5 S2: a[i+2] = b[i+2] * c[i+2];

6 S3: a[i+3] = b[i+3] * c[i+3];

7 }</pre>

```

Listing 7. Example after partial unrolling

In Listing 6, the loop body denoted by *L* is depicted in the rectangle. The loop L1 is subjected to a partial unrolling with a factor of 4, as specified by the directive *#pragma ACCEL parallel UF=4* hence S0 have to be expanded and replicated four times. The explicit unrolling of the loop is illustrated in Listing 7, where S0, S1, S2 and S3 represent the loop body L' of the Theorem B.10. The latency of the program in Listing 6 and 7 (which are equivalent) is greater or equal to  $\lfloor \frac{TC}{UF} \rfloor$ , in this case 2, multiply by the latency of the loop body L'. In this context, L' comprises statements S0, S1, S2, and S3. These four statements are independent of each other and can be executed concurrently. Therefore, the lower bound on latency for L' is equivalent to the latency of the multiplication operation.

Note this bound requires to build the operation graph for the whole loop body. This is straightforward for inner loops and/or fully unrolled loop nests, but impractical if the loop body contains other loops. We therefore define a weaker, but more practical, bound:

THEOREM 4.6 (MINIMAL LATENCY OF A PARTIALLY UNROLLED LOOP WITH FACTOR UF AND COMPLEX LOOP BODIES). Given a loop l with trip count  $TC_l$  and loop body L, and unroll factor  $UF \leq TC$ . Given available resources  $R_{op}$  and latencies  $L(op) \geq 1$ . Then the minimal latency of l if executed in a non-pipelined fashion is bounded by:

$$Lat_{R_{op}}^{l,S} \ge \lfloor TC/UF \rfloor * Lat_{R_{op}}^{L}$$

Consider the scenario of loop L0 within Listing 5, which has been unrolled by a factor denoted as  $UF \leq TC_{L0}$  where  $TC_{L0}$  is the trip count of L0. The latency for one iteration of S0 is denoted as  $Lat_{R_o}^{S0} > 0$ . In the absence of pipelining, the lower bound of the latency of this sub-loop body is:  $\lfloor TC_{L0}/UF \rfloor \times Lat_{R_o}^{S0}$ .

Vitis allows to do a reduction with a tree reduction in logarithmic time with the option "unsafe-math".

THEOREM 4.7 (MINIMAL LATENCY OF A PARTIALLY UNROLLED LOOP WITH FACTOR UF FOR REDUCTION LOOP WITH TREE REDUCTION). Given a reduction loop l with trip count  $TC_l$  and loop body L, and unroll factor  $UF \leq TC$ . Given available resources  $R_{op}$  and latencies  $L(op) \geq 1$ . Then the minimal latency of l, if executed in a non-pipelined fashion and the tree reduction is legal is bounded by:

$$Lat_{R_{op}}^{l,S} \geq \lfloor TC/UF \rfloor \times Lat_{R_{op}}^{L} \times \lfloor \log_{2}(UF) \rfloor$$

1 L1: for (i = 0; i < 8; i++) { 2 c += a[i]; 3 }

Listing 8. Example of code demonstrating a reduction, where a tree reduction technique can be applied, as depicted in Figure 1.

Fig. 1. Illustrating the concurrent execution depicted in Listing 12 through a tree reduction method, accomplished within logarithmic time.

Figure 1 represent the tree reduction of the Listing 12. Due to the reduction, we use a tree reduction in order to increase the parallelism of the reduction, and execute a loop of trip count n = 8 in  $\log_2(n) = 3$  iterations.

Automatic Hardware Pragma Insertion in High-Level Synthesis: A Non-Linear Programming Approach

4.2.3 Loop pipelining. Loop pipelining amounts to overlapping multiple iterations of the loop, so that the next iteration can start prior to the completion of the preceding one. The initiation interval (II) measures in cycles the delay between the start of two consecutive iterations. It is easy to prove our formula template accurately integrates the latency of pipelined loops with the *I* operator. We compute the minimal II in function of the dependencies of the pipelined loop and the iteration latency of the operations of the statements during the NLP generation. Let *RecMII* and *ResMII* be the recurrence constraints and the resource constraints of the pipelined loop, respectively. We have  $II \ge \max (ResMII, RecMII)$ .  $RecMII = \max_i \left\lceil \frac{delay(c_i)}{distance(c_i)} \right\rceil$  with  $delay(c_i)$  the total latency in dependency cycle  $c_i$  and  $distance(c_i)$  the total distance in dependency cycle  $c_i$ . We suppose that ResMII = 1, as we do not know how the resource will be used by the compiler. Hence, if the loop is a reduction loop then the  $II \ge \frac{IL_{reduction}}{1}$  with  $IL_{reduction}$  the iteration latency of the operation. For a kernel like the Listing 9 the  $II \ge \left\lceil \frac{IL}{2} \right\rceil$ .

, ,

1 for (j = 0; j < N; j++)

2 y[j] = y[j-2] + 3;</pre>

Listing 9. Demonstration of a code snippet showcasing a scenario where a loop pipelined with a dependency of distance 2 results in an initiation interval (*II*) that satisfies  $II \ge \lceil \frac{IL_+}{2} \rceil$ .

It follows a bound on the minimal latency of a pipelined loop:

THEOREM 4.8 (MINIMAL LATENCY OF A PIPELINED LOOP WITH KNOWN II). Given a loop l with trip count  $TC_l$  and loop body L. Given available resources  $R_{op}$  and latencies  $L(op) \ge 1$ . Then the minimal latency of l if executed in a pipelined fashion is bounded by:

$$Lat_{R_{op}}^{l,P} \ge Lat_{R_{op}}^{L} + II * (TC_{l} - 1)$$

In Listing 5, loop L1 is pipelined. However, loop L1 serves is a reduction loop for statement S2, meaning that we must await the completion of writing s[j] at iteration i before we can read and write again at iteration i + 1. Consequently, the initiation interval (*II*) is bounded by or greater than the latency (*IL*<sub>+</sub>) of the addition operation, which constitutes the reduction operation.

4.2.4 Loop pipelining and unrolling. A loop *l* with trip count  $TC_l$  can be pipelined and partially unrolled with  $UF < TC_l$ , in this case there is loop splitting where the trip count of the innermost loop equal to the unroll factor and the trip count of the outermost loop equal to  $\frac{TC_l}{UF}$ .

THEOREM 4.9 (MINIMAL LATENCY OF A PIPELINED LOOP WITH KNOWN II AND PARTIALLY UNROLLED). Given a loop l with trip count  $TC_l$ , partially unrolled by an unroll factor  $UF < TC_l$  and a loop body L. Given available resources  $R_{op}$  and latencies  $L(op) \ge 1$ . Given L' the loop body obtained by replicating UF times the original loop body L. Then the minimal latency of l if executed in a pipelined fashion is bounded by:

$$Lat_{R_{op}}^{l,P} \geq Lat_{R_{op}}^{L'} + II * (\frac{TC_l}{UF} - 1)$$

4.2.5 Non-Parallel, Non-Pipelined Loops. We continue with a trivial case: if the loop is not optimized by any directive (including any automatically inserted by the compilers), i.e., not parallelized nor pipelined, then every next iteration of the loop starts only after the end of the prior iteration.

Definition 4.10 (Lower bound on latency of a non-parallel, non-pipelined loop under resources constraints). Given a loop l with trip count  $TC_l$  which is neither pipelined nor parallelized, that is, iteration i + 1 starts after the full completion of iteration i, for all iterations. Given  $Lat^L_{R_{op}}$  the minimal latency of its loop body. Then

$$Lat_{R_{op}}^{l} \geq TC_{l} * Lat_{R_{op}}^{L}$$

4.2.6 *Coarse-Grained parallelization.* Coarse-grained parallelization is a performance enhancement technique involving the unrolling of a loop which iterates a loop body not fully unrolled i.e., containing at least a pipelined loop or a loop executed sequentially. It is therefore impossible to do a coarse-grained parallelization with a reduction loop because the *n* sub loop body are dependent on each other.

It follows a bound on the minimal latency of a coarse-grained unrolled loop:

,,

THEOREM 4.11 (MINIMAL LATENCY OF COARSE-GRAINED UNROLLED LOOP). Given a loop l, which is not a reduction loop, with trip count  $TC_l$ , an unroll factor  $UF \leq TC_l$  and L the loop body iterated by the loop l with a latency lower bound  $Lat_{R_{op}}^{L}$ . Given available resources  $R_{op}$  and latencies  $L(op) \geq 1$ . Given L' the loop body obtained by replicating UF times the original loop body L. Then the minimal latency of l if executed in a non-pipelined fashion is bounded by:

$$Lat_{R_{op}}^{l,S} \ge \lfloor TC/UF \rfloor \times Lat_{R_{op}}^{L'}$$

4.2.7 Program latency lower bound under resource constraints. We now focus on the latency lower bound of a program, under resource constraints. This bound takes into account the limitations imposed by available resources, which can significantly affect the achievable performance. We assume here that the resources consumed are only consumed by the computing units and resource use by the computational unit of one operation can not be reused by the computational unit of another operation executing at the same time. We also assume that the compilers have implemented the pragma configuration given as input.

For DSPs we suppose we have a perfect reuse i.e., that the computation units for the same operation can be reused as soon as the computation unit is not in use. Under-estimating the resources used is fundamental to proving the latency lower bound, as otherwise another design that consumes less resources than predicted may be feasible, itself possibly leading to a better latency.

THEOREM 4.12. Given a loop body L, the set of set of statements  $S_{seq}$  non executed in parallel,  $\#L_{op}^{s}$  the number of operations op for the statements s,  $DSP_{op}$  the number of resources (DSPs) used for the operation op,  $MCU_{op}^{s}$  the maximal number of computational units the statement s can use in parallel at any given time, and the configuration of pragma  $PV_i$  for each loop. The minimal number of resource (DSPs) consumed,  $R_{used}^{min}$ , by L for the pragma configuration is the sum, for each operation, of the maximum number of DSPs used in parallel by a statement. This corresponds to:

$$R_{used}^{min} = \sum_{op} \max_{S \in S_{seq}} (\sum_{s \in S} \#L_{op}^{s} \times DSP_{op} \times MCU_{op}^{s})$$

Given a program and the available resource of DSP  $DSP_{avail}$ , if  $R_{used}^{min} < DSP_{avail}$  the lower bound is valid and the program does not over-utilize the resources.

In Listing 5, statements S0 and S1 entail no DSP usage as they solely serve for initialization purposes. S2 and S3 undergo unrolling N times and operate independently, enabling parallel execution. Particularly, S3 necessitates a tree reduction since it acts as a reduction for loop *L*2.

Assuming 1 DSP for addition and 2 for multiplication (denoted as  $DSP_+$  and  $DSP_*$  respectively), the maximum number of computational units utilized by S2 and S3 for both addition and multiplication is N. Therefore,  $MCU_+^{S2}$  =

$N, MCU_*^{S2} = N, MCU_+^{S3} = N$ , and  $MCU_*^{S3} = N$ . Furthermore, each statement entails only one addition and one multiplication, hence  $\#L_+^{S2} = 1, \#L_+^{S2} = 1, \#L_+^{S3} = 1$ , and  $\#L_*^{S3} = 1$ .

Consequently, the minimum number of DSPs utilized by Listing 5 is  $N \times (1 + 2) \times 2$ .

4.2.8 *Memory transfer.* AMD/Xilinx Merlin manages automatically the memory transfer. The memory transfer and computation are not overlap (no dataflow) hence the latency is the sum of the latency of computation and communication. We assume that for each array the contents of the array are in the same DRAM bank.

THEOREM 4.13 (LOWER BOUND OF THE MEMORY TRANSFER LATENCY FOR AN ARRAY). Given a loop body L, the set of array  $\mathcal{A}$ , an array  $a \in \mathcal{A}$ , and  $LAT_a^{mem}$  the latency to transfer the array a from off-chip to on-chip (inputs) and from on-chip to off-chip (outputs).  $\forall a \in \mathcal{A}$ ,  $LAT_a^{mem} \geq (\mathbb{1}_{a \in V_O^L} + \mathbb{1}_{a \in V_I^L}) \times footprint_a/max\_burst\_size$ . With  $\mathbb{1}_{cond} = 1$  if cond = true else 0.

Within Listing 5, the matrix A is solely read and possesses a footprint of  $N \times M \times 32$  bits. Given the FPGA's limitation to process a maximum of 512 bits per cycle, the latency required for transferring A amounts to  $\frac{N \times M}{16}$  cycles.

THEOREM 4.14 (LOWER BOUND OF THE MEMORY TRANSFER LATENCY). Given a loop body L, the set of array  $\mathcal{A}$ , the number of cycles to transfer the array a is bounded by  $\max_{a \in \mathcal{A}} (\mathbb{1}_{a \in V_{a}^{L}} + \mathbb{1}_{a \in V_{a}^{L}}) \times footprint_{a}/max_{burst_size}$ .

In Listing 5, when transferring all arrays before any computation, we can concurrently transfer each array (assuming they are in different DRAM banks). The primary bottleneck arises from the transfer of array *A*, which incurs a latency of  $\frac{N \times M}{16}$  cycles. Upon program completion, arrays *s* and *q* need to be transferred back to DRAM, with a minimal latency of max( $\frac{N}{16}, \frac{M}{16}$ ) cycles each. Thus, the total communication latency amounts to  $\frac{N \times M}{16} + \max(\frac{N}{16}, \frac{M}{16})$  cycles.

# 4.3 Summary

By composing all the theorems, this allows us to end up with the final latency lower bound of the program which is presented in theorems B.20 for the computation and B.21 for the computation and communication.

THEOREM 4.15 (COMPUTATION LATENCY LOWER BOUND OF A PROGRAM). Given available resource  $DSP_{avail}$ , the properties vector  $\vec{PV}_i$  for each loop and a program which contains a loop body L. The properties vector allows to give all the information concerning the trip counts and the II of the pipelined loops and to decompose the loop body L with a set of loops  $\mathcal{L}_L^{non \ reduction}$  potentially coarse-grained unrolled with  $\forall l \in \mathcal{L}_L$ ,  $UF_l$  and a set of reduction loops executed sequentially  $\mathcal{L}_L^{reduction}$  which iterates a loop body  $L_{pip}$ . By recursion the loop body  $L_{pip}$  contains a pipelined loop  $l_{pip}$  which iterate a loop body  $L_{fg}$  fully unrolled. The loop body  $L_{fg}$  contains operations which can be done in parallel with a latency  $Lat_{R_{op}}^{L_{par}}$  and operations which are reduction originally iterated by the loops  $\mathcal{L}_{Lg}^{reduction}$  with a latency  $Lat_{Lseq}$ .

The computation latency lower bound of L, which respected  $DSP_{ued}^{mig} \leq DSP_{avail}$ , executed with tree reduction is:

$$Lat_{R_{op}}^{L} \geq \prod_{l \in \mathcal{L}_{L}^{par}} \frac{TC_{l}}{UF_{l}} \times \prod_{l \in \mathcal{L}_{L}^{reduction}} TC_{l} \times Lat_{R_{op}}^{L_{pip}}$$

with

$$Lat_{R_{op}}^{L_{pip}} = (Lat_{R_{op}}^{L_{fg}} + II \times (\frac{TC_{l_{pip}}}{l_{pip} - UF} - 1)) \text{ and } Lat_{R_{op}}^{L_{fg}} = Lat_{L_{par}} + Lat_{L_{seq}} \times \prod_{l \in \mathcal{L}_{L_{fg}}^{reduction}} \frac{TC_l}{UF_l} \times \log_2(UF_l).$$

In Listing 5, let's denote the loop body with loop *L*0 and statement *S*0 as *LB*0, and the one with loops *L*1 and *L*2, along with statements *S*1, *S*2, and *S*3, as *LB*1.

For *LB*0, where the loop is unrolled with a factor uf and no dependency exists between loop iterations, the latency is bounded by  $\frac{N}{uf} \times 1$ , assuming the initialization takes at least one cycle.

Regarding *LB*1, loop *L*2 is fully unrolled, with no dependencies between iterations for statement *S*2. As there is no dependency between *S*2 and *S*3, they can be executed in parallel, and the latency of the unrolled part equals the critical path, which is the maximum between the unrolled parts of *S*2 and *S*3 in this scenario. However, for statement *S*3, despite the absence of dependencies among multiplication operations enabling parallel execution, a tree reduction is involved. Given the pipelined nature of loop *L*1, functioning as a reduction for statement *S*2, we observe  $II > IL_+$ , where  $IL_+$  denotes the latency of the reduction operation. Consequently, the latency of *LB*1 is bounded by (max( $IL_+ + IL_*, IL_+ \log_2(N) \times IL_+) + IL_+ \times (M - 1)$ ).

THEOREM 4.16 (LATENCY LOWER BOUND OF A PROGRAM OPTIMIZED WITH MERLIN PRAGMAS). Given available resource  $DSP_{avail}$  and a program which contains a loop body L with a computation latency  $Lat_L^{computation}$  and a communication latency  $Lat_L^{communication}$ .

The lower bound for L which respected  $DSP_{ued}^{min} \leq DSP_{avail}$  and where the computation and communication can not be overlap is:

$$Lat_L = Lat_L^{computation} + Lat_L^{communication}$$

#### 5 NON-LINEAR FORMULATION FOR PRAGMA INSERTION

We now present the complete set of constraints and variables employed to encode the latency and resource model as a non-linear program. This section presents a modeling of section 4 in the practical case.

Let  $\mathcal{L}$  be the set of loops,  $\mathcal{A}$  the set of arrays,  $\mathcal{S}$  the set of statements and  $O_s$  the operations of the statements s. In order to have an accurate model we distinguish for each statement the operation which can be done in parallel, i.e., does not have any loop-carried dependence,  $O_{s_{par}}$  and the reduction operations, i.e., associative/commutative operators to reduce one or more values into a single value, leading to loop-carried dependencies,  $O_{s_{red}}$ .

Let  $\mathcal{P}$  be the set of different possible pipeline configurations. Let  $\forall p \in \mathcal{P}$  define  $\mathcal{L}_{pip}^{p}$  the set of loops pipelined and  $\forall l \in \mathcal{L}_{pip}^{p}, \mathcal{L}_{under\_pip_{l}}^{p}$  the set of loops under a loop pipelined and  $\mathcal{L}_{above\_pip_{l}}^{p}$  the set of loops above the loop pipelined l. Let  $\forall s \in S$  define the set of nested loops which iterate the statement  $s, \mathcal{L}_{s}. \forall a \in \mathcal{A}$  and for d a dimension of the array a, let  $C_{a_{d}}$  be the set of loops which iterates the array a at the dimension  $d. \forall l \in \mathcal{L}$ , let designate  $d_{l}$  the maximum dependency distance of the loop l. And let  $II_{s}$  be the II of the loop pipelined for the statement s.

The II for each loop, the dependencies, the properties of the loops, the TC, the iteration latency of the parallel operations and the reduction operations and the number of DSPs per operation per statements are computed at compile time with PolyOpt-HLS [29] and used as constants in the NLP problem.

## 5.1 Variables

,,

Variables in the formulation correspond to  $PV_l$  attributes. We consider the possibilities of pipelining (Eq. 3), unrolling (Eq. 1), and tiling (Eq. 2) for each loop. Additionally, we include the possibility of caching an array that is iterated over by the loop (Eq. 4).

Table 4, summarize the sets, variable and constants we use.

Automatic Hardware Pragma Insertion in High-Level Synthesis: A Non-Linear Programming Approach

| Set                                                                                           | Description                                                                                  |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| $\mathcal{L}$                                                                                 | the set of loops                                                                             |

| Я                                                                                             | the set of arrays                                                                            |

| S                                                                                             | the set of statements                                                                        |

| $O_s$                                                                                         | the list of operations of the statements s                                                   |

| $O_{s_{par}}$                                                                                 | the operation which can be done in parallel, i.e., does not have any loop-carried dependence |

| r                                                                                             | the set of different possible pipeline configurations                                        |

| $\mathcal{L}_{pip}^{p}$                                                                       | the set of loops pipelined                                                                   |

| $\mathcal{L}_{pip}^{p}$<br>$\mathcal{L}_{under_pip_l}^{p}$<br>$\mathcal{L}_{above_pip_l}^{p}$ | the set of loops under a loop pipelined                                                      |

| $\mathcal{L}^{p}_{above \ pip_{l}}$                                                           | the set of loops above the loop pipelined $l$                                                |

| $\mathcal{L}_{s}$                                                                             | the set of nested loops which iterate the statement s                                        |

| $C_{a_d}$                                                                                     | the set of loops which iterates the array $a$ at the dimension $d$                           |

| $d_l$                                                                                         | the maximum dependency distance of the loop <i>l</i>                                         |

| Variable                                                                                      | Description                                                                                  |

| loop <sub>l</sub> _UF                                                                         | Unroll factor of the loop <i>l</i>                                                           |

| loop <sub>l</sub> _tile                                                                       | TC of the innermost loop after strip-mining of the loop $l$                                  |

| loop <sub>l</sub> _pip                                                                        | Boolean to know if the loop <i>l</i> is pipelined                                            |

| loop <sub>l</sub> _cache_array_a                                                              | Boolean to know the the array $a$ is transferred on-chip before the loop $l$                 |

| Constant                                                                                      | Description                                                                                  |

| $TC_l$                                                                                        | Trip Count of the loop <i>l</i>                                                              |

| II <sub>l</sub>                                                                               | II of the loop <i>l</i>                                                                      |

| ILpar                                                                                         | Iteration Latency of the operations whitout dependencies of the statement s                  |

| ILred                                                                                         | Iteration Latency of the operations whit dependencies of the statement s                     |

| $DSP_{s_{op}}$                                                                                | Number of DSP used for the statement <i>s</i> for the operation <i>op</i>                    |

| DSP <sub>available</sub>                                                                      | Number of DSP available for the FPGA used                                                    |

| MAX_PARTITIONING                                                                              | Maximum array partitioning defined by the user or the DSE (cf. Section 6)                    |

| footprint_arraya_loop <sub>l</sub>                                                            | Footprint of the array $a$ if transferred on-chip before the loop $l$                        |

, ,

Table 4. Description of the sets, variables, and constants utilized in the formulation of the Nonlinear Problem (NLP) aimed at modeling latency and resource consumption of a design

# 5.2 Modeling Compiler Transformations

Now that we have defined our design space, we need to constrain the space by removing infeasible cases and those that do not comply with the rules of the compilers.

*Pipeline Rules.* Vitis HLS unrolls all loops under the pipelined loop. This implies that all loop *l* under the pipelined loop must have  $loop_{l}_UF == TC_l$  (Eq. 15). Considering this constraint, it is important to note that for each statement, only one of the loops that iterate the statement can have a pragma pipeline (Eq. 5). If multiple pipelined loops were present, the loops beneath the first pipelined loop would be unrolled instead.

*Memory Transfer Rules.* Merlin automates the process of transferring data on-chip and applying array partitioning. The tool caches data on-chip and packs it in chunks of up to 512 bits, enabling efficient transfer speed. When the data is already present on-chip it can be reused provided that resource constraints are satisfied. The compiler caches on-chip the data only above the loop pipelined (Eq. 14).

Dependencies. Loop-carried dependencies are managed using constraints (Eq 8). If a loop has a dependency distance of n, this means that if we unroll with an unroll factor uf > n this is equivalent to unrolling the loop with a factor

uf = n because the statements corresponding to the iteration  $\{uf + 1, ..., n\}$  will be executed only after the first n statements are executed due to the dependency. Loop-independent data dependencies are managed at the objective function, as elaborated in Section 5.4.

*Supplementary Rules.* In addition, we add the constraints for the maximum unrolling (Eq. 10), the divisibility of the problem size of the unroll factors (Eq. 6), the tile size (Eq. 7) and the maximum array partitioning (Eq. 13). For this last, this corresponds to adding an upper bound to the product of the UF of all the loops which iterate the same array on different dimensions.

During our DSE, we can force the solution to be fine-grained. In this case we add a constraint where the loop above the loop pipelined has a UF of 1, i.e., for all loop *l* above the pipelined loop  $loop_{l}_{-}UF == 1$  (Eq. 9). We also constrain the resources, modeling their sharing optimistically. We consider the number of DSPs (Eq. 11) and on-chip memory (Eq. 12) used. As the consumption of DSPs can be difficult to estimate due to resource sharing we utilize an optimistic estimate, which considers a perfect reuse/sharing: as soon as a computation unit is free, its resource can be reused.

## 5.3 Constraints

, ,

- $\forall l \in \mathcal{L}, 1 \le loop_l\_UF \le TC_l \tag{1}$

- $\forall l \in \mathcal{L}, 1 \le loop_l\_tile \le TC_l \tag{2}$

- $\forall l \in \mathcal{L}, loop_{l}\_pip \in \{0, 1\}$ (3)

- $\forall l \in \mathcal{L}, \forall a \in \mathcal{A}, loop_l\_cache\_array_a \in \{0, 1\}$ (4)

$$\forall s \in \mathcal{S}, \sum_{l \in \mathcal{L}_s} loop_{l\_}pip \le 1$$

(5)

$$\forall l \in \mathcal{L}, loop_l\_UF\%TC_l == 0 \tag{6}$$

$$\forall l \in \mathcal{L}, loop_l\_tile\%TC_l == 0 \tag{7}$$

$$\forall l \in \mathcal{L}, \text{ if } dd_l > 1, loop_l\_UF \le d_l \tag{8}$$

$$\forall l \in \mathcal{L}, \forall l' \in \mathcal{L}_{above\_l}, loop_{l\_pip} * loop_{l'\_}UF <= 1$$

(9)

$$\forall s \in \mathcal{S}, \prod_{l \in L_s} loop_l\_UF \le MAX\_PARTITIONING$$

(10)

$$DSPs\_used_{optimistic} = \sum_{op \in \{+, -, *, /\}} \max_{s \in S} (DSP_{s_{op}} / II_s) \le DSP_{available}$$

(11)

$$\sum_{a \in \mathcal{A}} \sum_{l \in \mathcal{L}} loop_{l}\_cache\_array_{a}$$

$$\times footprint\_array_{a}\_loop_{l} \le Mem$$

(12)

$$\forall a \in \mathcal{A}, \forall (d, d') \in \mathbb{N}^2 \text{ with } d \neq d', \forall l \in C_{a_d}, \forall l' \in C_{a_{d'}},$$

(13)

$$loop_1 UF \times loop_{1'} UF \leq MAX PARTITIONING$$

Automatic Hardware Pragma Insertion in High-Level Synthesis: A Non-Linear Programming Approach

$$\begin{cases} \forall p \in \mathcal{P}, \forall lp \in \mathcal{L}_{pip}^{p}, \forall lbp \in \mathcal{L}_{under\_pip_{lp}} \forall a \in \mathcal{A}, \\ loop_{lbp\_}cache\_array_{a} == 0 \end{cases}$$

$$\begin{cases} \forall p \in \mathcal{P}, \forall lp \in \mathcal{L}_{pip}^{p}, \forall lbp \in \mathcal{L}_{under\_pip_{lp}}, \\ loop_{lp} \times loop_{lbp\_}UF == loop_{lp} \times TC_{lbp} \end{cases}$$

(14)

$$\end{cases}$$

$$\int_{a}^{b} \int_{a}^{b} \int_{a$$

$$loop_{lp} \times loop_{lbp} UF == loop_{lp} \times TC_{lbp}$$

$$(15)$$

# 5.4 Objective function

Lastly, we need to define the objective function  $(ob_{i-func})$  that supports fine-grained and coarse-grained parallelism. Fine-grained parallelism involves duplicating a specific statement(s), while coarse-grained parallelism duplicates modules, including statements and loops. However, it may not always be feasible to achieve parallelism based on the characteristics of the loops and the level of parallelism required. Therefore, we distinguish between parallel and reduction loops. A parallel loop can be coarse and fine-grained unrolled, whereas a reduction loop can only be fine-grained unrolled with a tree reduction process that operates in logarithmic time.

As the pragmas cache are part of the space we compute the communication latency with these pragmas. If more than one array is transferred above the same loop we take the maximum as Merlin transferred them in parallel. To ensure these properties, we formulate the objective function for each pipeline configuration. The objective function uses the combined latencies of communication and computation. When using Merlin, communication and computation do not overlap, but communication tasks can overlap when they occur consecutively in the code at the same level. Consequently, for each loop, where two arrays are transferred consecutively within the loop, we calculate the sum of the maximum latencies for these transferred arrays (Lmem).

In every loop nest, there will invariably be a pipeline loop due to either user-inserted or compiler-inserted instructions (AMD/Xilinx Merlin and Vitis automatically insert the pragma pipeline if it is not done by the user or the previous compiler). Therefore, the objective function takes the following form:  $TC_{ap} \times (IL + II \times (\frac{TC}{ILF} - 1))$ , where  $TC_{ap}$  includes the loops situated above the pipeline. Parallel loops above the pipeline can be coarse-grained parallelized. The iteration latency within the unrolled loop body is divided into either reduction operations or non-reduction operations, as reduction operations require logarithmic time for the reduction process. The variable IL encompasses the latencies of the statements found within the pipelined loop body. Independent statements can be executed in parallel and statements with dependencies are summed, as detailed in Section 4.1.

$$\begin{split} TC_{ap} &= \prod_{l \in \mathcal{L}_{above\_pip}} \frac{TC_l}{loop_l\_UF} \times \prod_{l \in \mathcal{L}_{above\_pip}} TC_l \\ IL &= IL_{par} + IL_{seq} \times \prod_{l \in \mathcal{L}_{under\_pip}} \frac{TC_l}{loop_l\_UF} \times \log_2(loop_l\_UF) \\ L_{mem} &= \sum_{l \in \mathcal{L}} \max_{a \in \mathcal{A}} (loop_l\_cache_a \times footprinta\_loop_l) \\ obj\_func &= TC_{ap} \times (IL + II \times (\frac{TC_{lp}}{loop_l\_UF} - 1)) + L_{mem} \end{split}$$

#### 5.5 Example

```

Loop0: for(i=0; i<2100; i++)</pre>

S0:y[i] = 0;

3 Loop1: for(i=0; i<1900; i++) {</pre>

S1:t[i] = 0;

4

Loop2: for(j=0; j<2100; j++)

```

```

6 S2:t[i]+=A[i][j]*x[j];

7 Loop3: for(j=0; j<2100; j++)

8 S3:y[j]+=A[i][j]*t[i];

9 }

```

,,

Listing 10. AtAx code for Large problem size: t = A \* x; y = A \* t

We now employ the AtAx kernel as an illustration. S0 and S3 do not have inter-iteration dependencies within their respective loops, namely *Loop*0 and *Loop*3. Therefore, it is possible to pipeline *Loop*0 and *Loop*3 with an  $II \ge 1$ . In other words, for all iterations within these loops, there are no dependencies on previous iterations within the same loop. Loop1 and Loop2 are reduction loops, and the reduction operation is an addition which has an IL of  $IL_+$  cycles. So the II  $\ge IL_+$ . If loop1 is pipelined, there is a dependency between S1, S2 and S3 Between S1 and S2 the distance is 1, so we just add IL\_S1 and IL\_S2. Between S2 and S3 the distance is log(N) so the final equation will be IL\_S1 + IL\_S2 \* log(N) + IL\_S3 for the loop body cycle. If statements can be run at the same time (i.e., there is no dependency) it is a max instead of an addition. If we encounter code like for(j = 2; j < N; j + )y[j] = y[j - 2] + 3;, a straightforward approach to handling this type of dependency is to impose a constraint such as  $loop_LUF \le 2$ , which is represented by equation 8. In this case, due to dependencies an UF > 2 is similar to UF = 2.

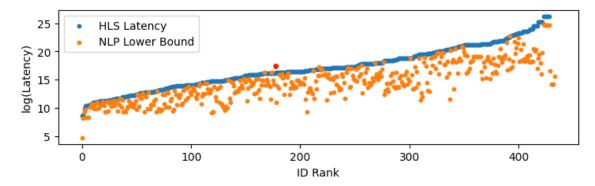

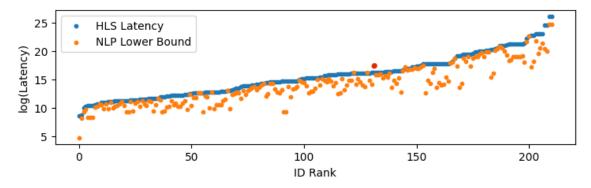

# 6 DESIGN SPACE EXPLORATION