# DSAGEN: Synthesizing Programmable Spatial Accelerators

Jian Weng, Sihao Liu, Vidushi Dadu, Zhengrong Wang, Preyas Shah, Tony Nowatzki

University of California, Los Angeles

May 15<sup>th</sup>, 2020

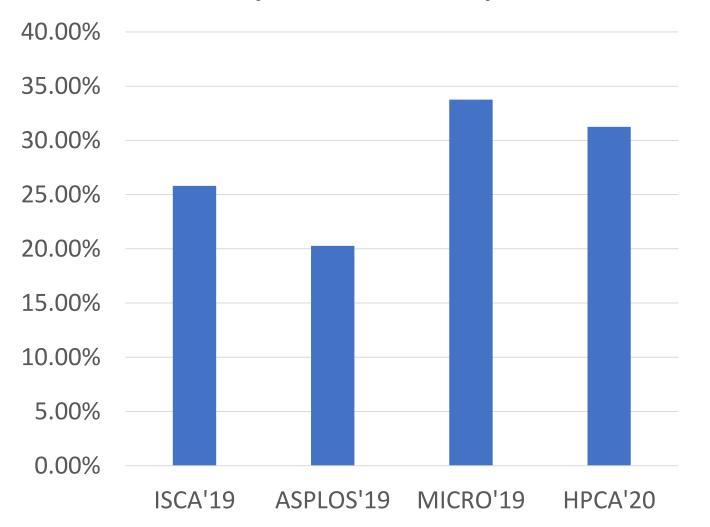

# Specialized Accelerators

Specialized architecture often occupies 1/5~1/3 of publications in top conferences.

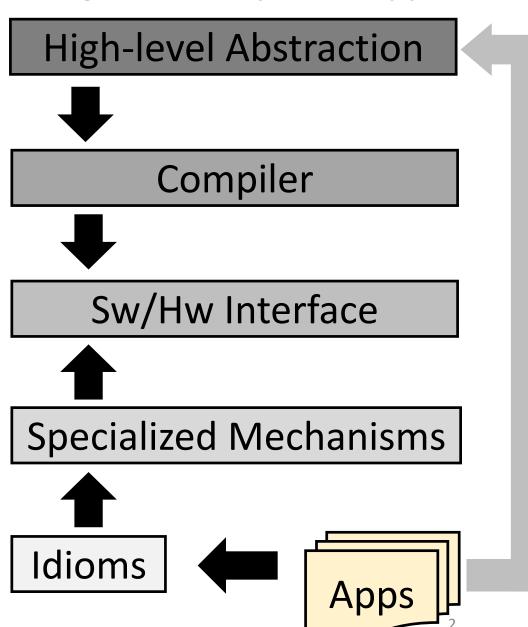

#### **Existing Domain-Specific Approach:**

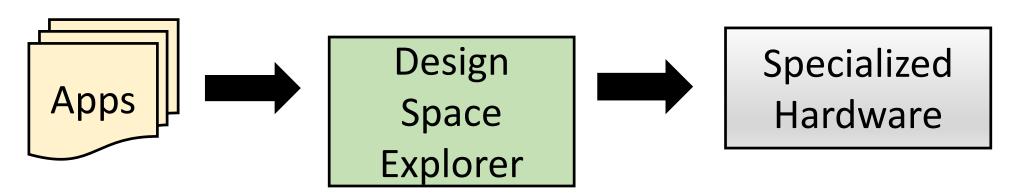

# DSAGEN: <u>Decoupled Spatial Accelerator Generator</u>

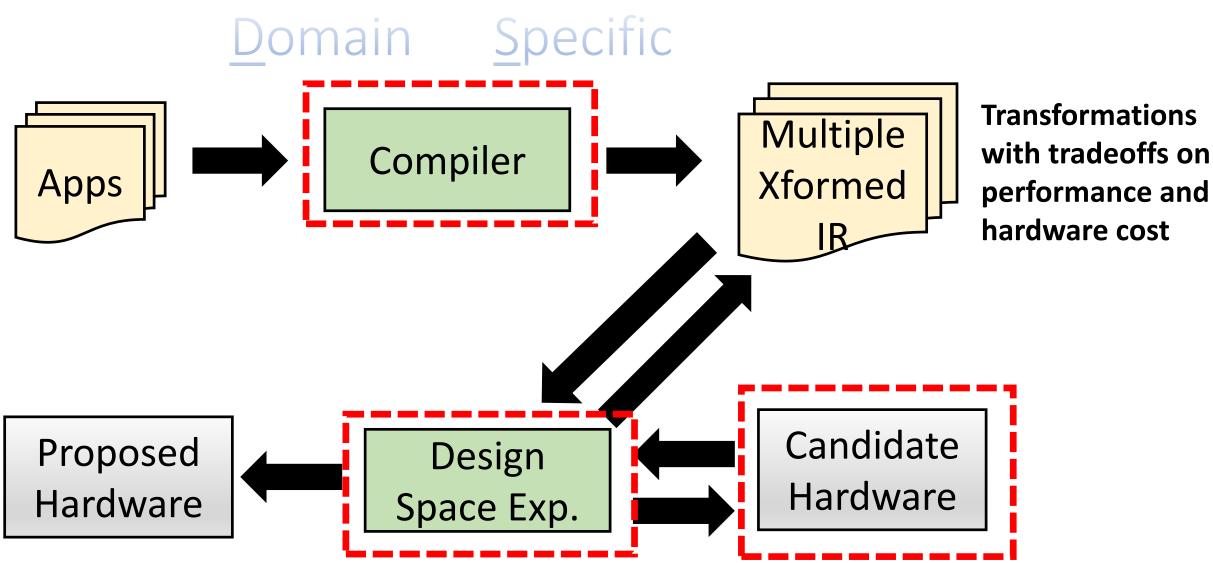

<u>Domain</u> <u>Specific</u>

# DSAGEN: <u>Decoupled Spatial Accelerator Generator</u>

#### Outline

- Design Space Decoupled-Spatial Architecture

- Insight from Prior Work

- The Programming Paradigm

- Design Space: Hardware Primitives (& Composition)

- Compilation

- Design Space Exploration

- Evaluation

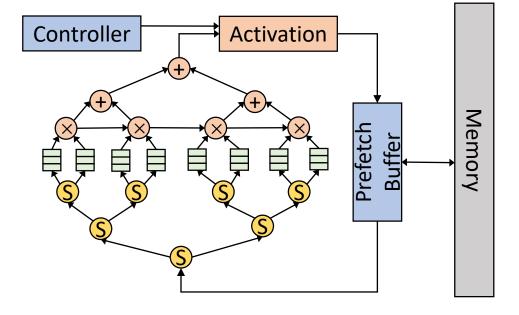

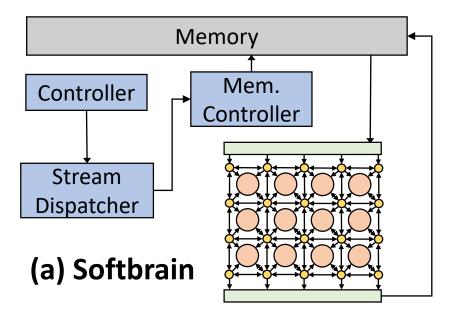

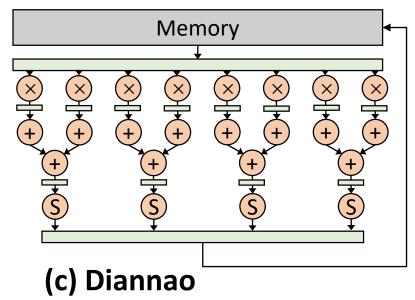

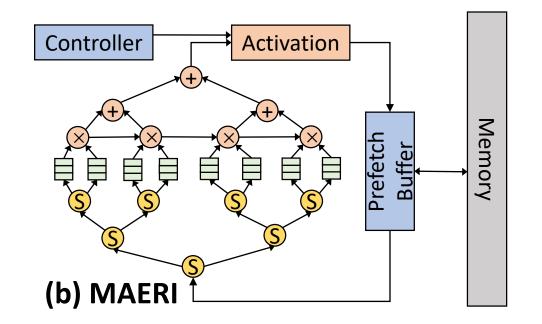

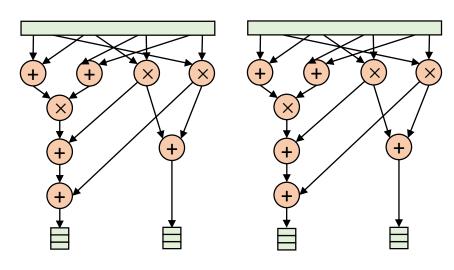

#### (a) ASPLOS18-MAERI

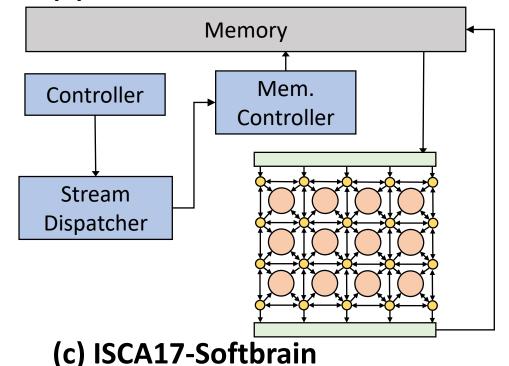

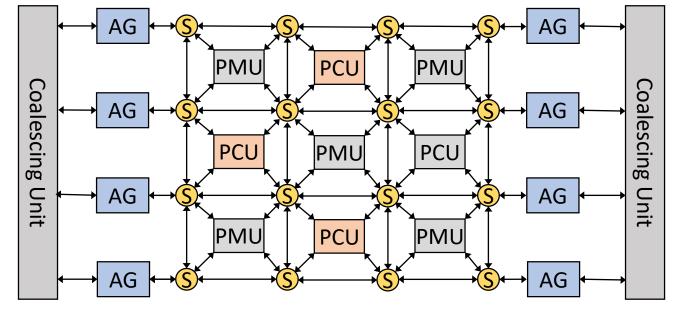

(b) ISCA17-Plasticine

- Decoupled-Spatial Paradigm

- Decoupled Compute/Memory<sub>Func. Unit</sub>

- Spatially exposed resources Memory

- Design Space

- Composing hardware with simple primitives

- Architecture Description Graph

Switch

Control

Sync. Elem.

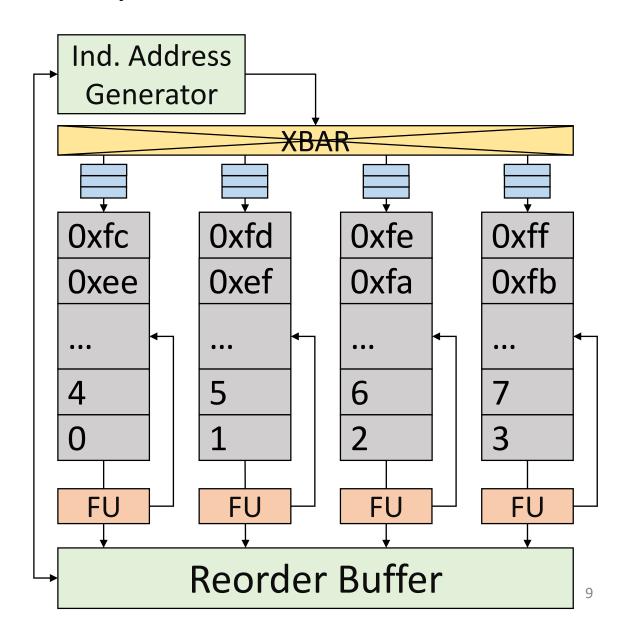

## Background: Decoupled-Spatial Architecture

## Hardware Primitives: Processing Element & Switch

| Hardware<br>Cost: Low    | Dedicated (=1)                                                               | Shared (>1) High                                                                  |                                                    |

|--------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|

| Statically<br>Scheduled  | "Systolic" 1x Area + No contention - Harder to map - Higher power *Softbrain | "CGRA" 2.6x Area + Better resource utilization - Harder to map *Conventional CGRA | Instruction Function Degisters                     |

| Dynamically<br>Scheduled | "Ordered Dataflow" 2.1x Area + Better flexibility *SPU                       | "Tagged Dataflow" 5.8x Area + Better flexibility + Better resource                | Function Unit Register File  Instruction Scheduler |

| High                     |                                                                              | <pre>utilization *Triggered Instruction</pre>                                     |                                                    |

#### Hardware Primitives: Memory

- Memory

- Size

- Bandwidth

- Indirect Support

- a[b[i]]

- Atomic Update

- a[b[i]] += 1

# Examples of ADG

(d) Data Path of Complex Mul.

#### Outline

- Decoupled-Spatial Architecture

- Compilation

- High-Level Abstraction

- Hardware-Aware Modular Compilation

- Design Space Exploration

- Evaluation

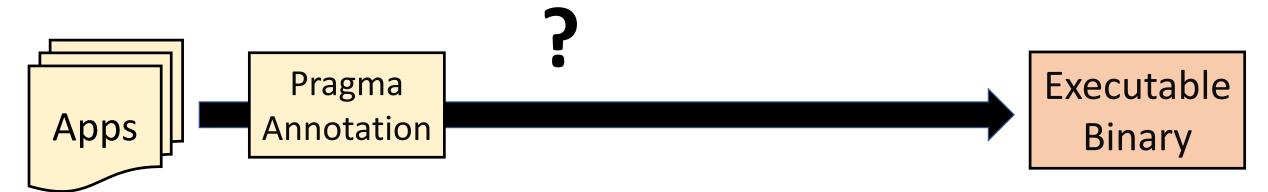

## Compiling High-Level Lang. to Decoupled Spatial

How to abstract diverse underlying features with a unified high-level interface?

- Programmer Hints

- Which code regions are offloaded onto the spatial accelerator.

- Which memory accesses can be decoupled intrinsics.

- Which offloaded regions should be concurrent.

#### An example of pragma annotation

```

#pragma config ← The offloaded region in this compound body are concurrent

#pragma stream ← The memory accesses below √ c[0:n] stricted

for (i=0; i<n; ++i)

#pragma offload ← The computational instructions be few will be offloaded

for (j=0; j<n; ++j)

a[i*n+j] += b[c[j]] * d[i*n+j];

```

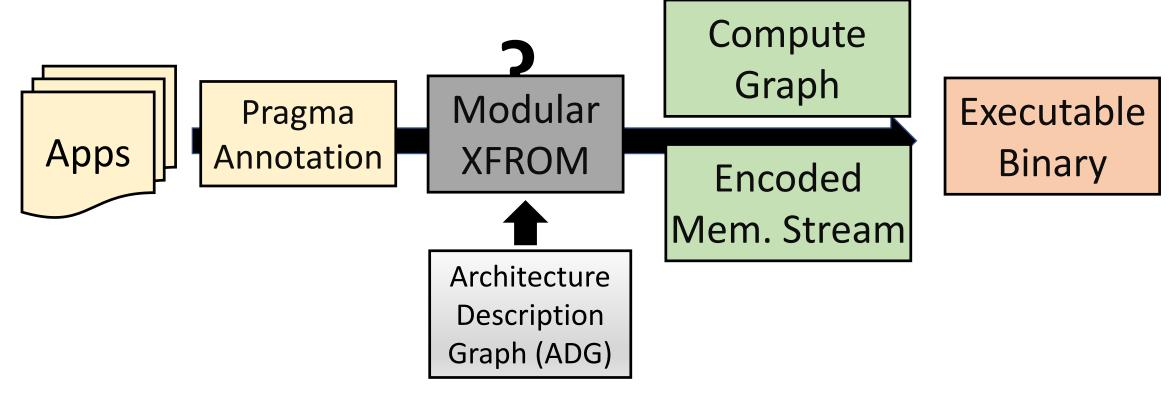

# Compiling High-Level Lang. to Decoupled Spatial

#### How to hide the diversity of underlying hardware?

- Modular Transformation

- Specialized Hardware features often dictate the code transformation

- A fallback is required when the hardware feature is not available

#### Modular Transformation

```

Inspect the hardware features to generate

c[0:n]

corresponding version of indirect memory

#pragma config

d[0:n] ||

a[0:n]

#pragma stream

// With indirect support

for (i=0; i<n; ++i)

Read c[0:n], stream0

Indirect b, stream0, stream1

#pragma offload

a[0:n]

for (j=0; j<n; ++j)

// Without indirect support

for (j=0; j<n; ++j)

a[i*n+j] += b[c[j]] * d[i*n+j];

Scalar b[c[j]], stream0

```

# Compiling High-Level Lang. to Decoupled Spatial

Modular XFROM Compute Graph

Encoded Mem. Stream Executable Binary

How is the dependence graph of computational instructions mapped?

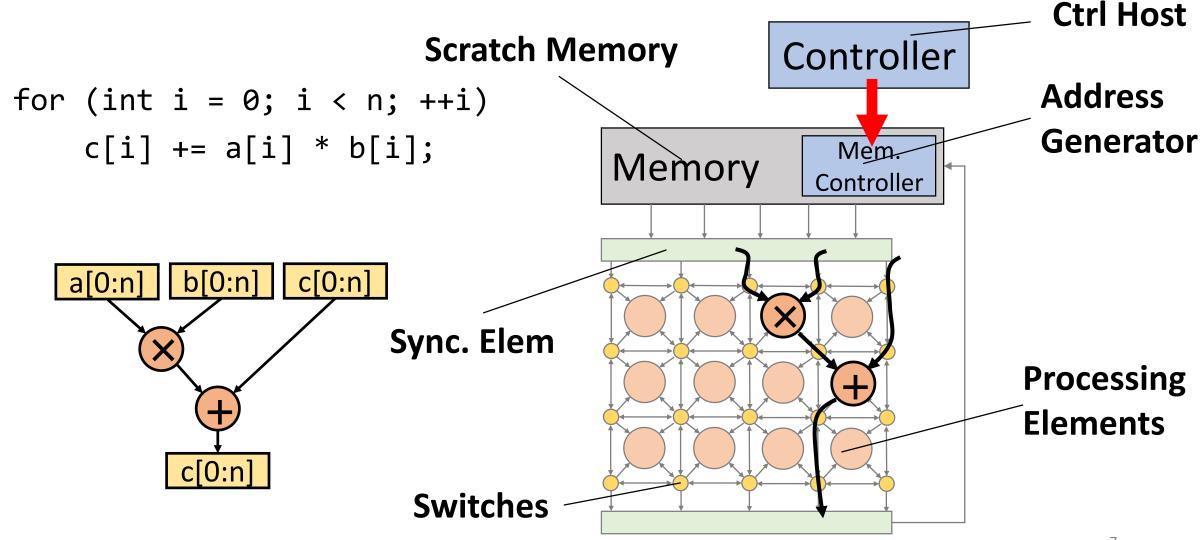

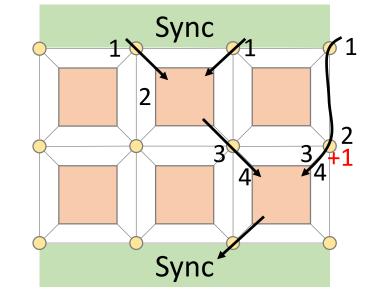

## Spatial Mapping

How is the dependence graph of computational instructions mapped?

- 1. Placement: Map instruction to PE's with corresponding capability.

- 2. Routing: Routing the dependence edges thru the spatial network.

- 3. Timing: If necessary, balance the timing of data arrival

- If one of 1-3 is not successful, revert some nodes and repeat 123

#### Outline

- Decoupled-Spatial Architecture

- Compilation

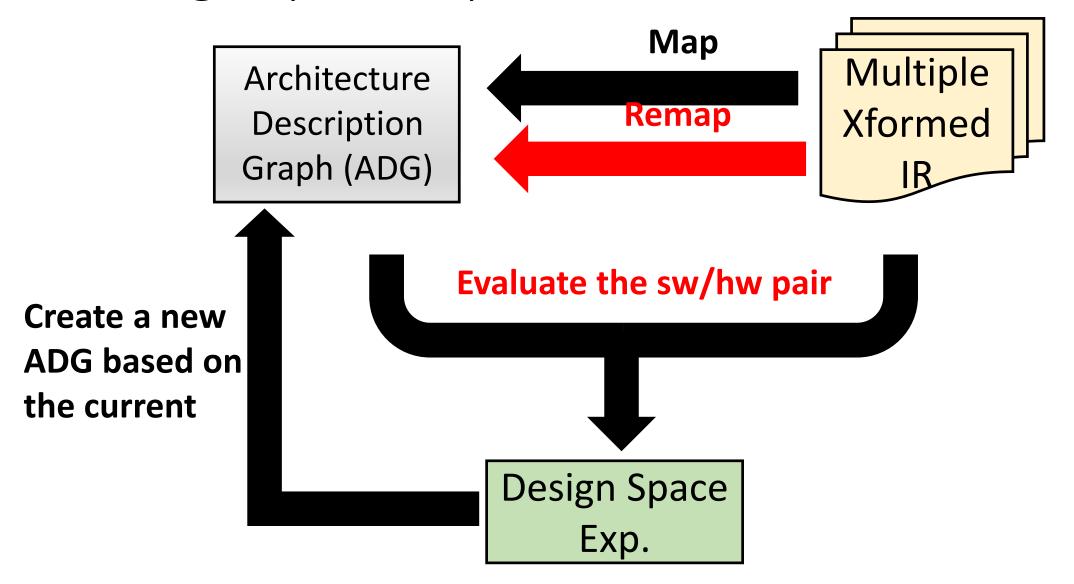

- Design Space Exploration

- Drive the Search

- Evaluating Design Points

- Repairing the Mapping

- Evaluation

#### Design Space Exploration

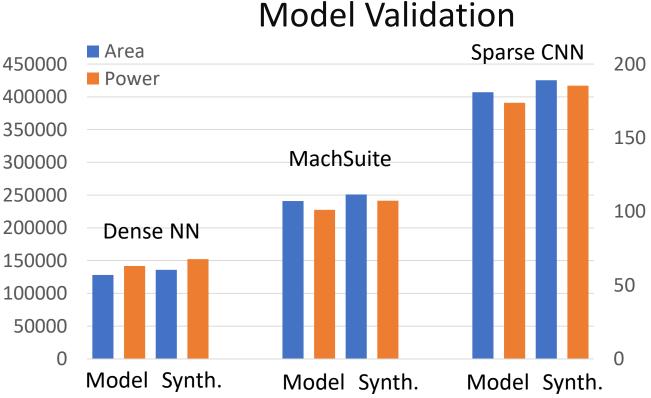

#### **Estimation Model**

- Performance

- Spatial architecture essentially enables hardware specialized sw-pipelining

- The ratio of data availability determines the performance 350000

- Perf=#Inst \* (Activity Ratio)

The model has mean performance error of 7%, and with maximum error 30%.

- Power/Area

- Synthesis can be time consuming

- A regression model can predict the trend of hardware cost

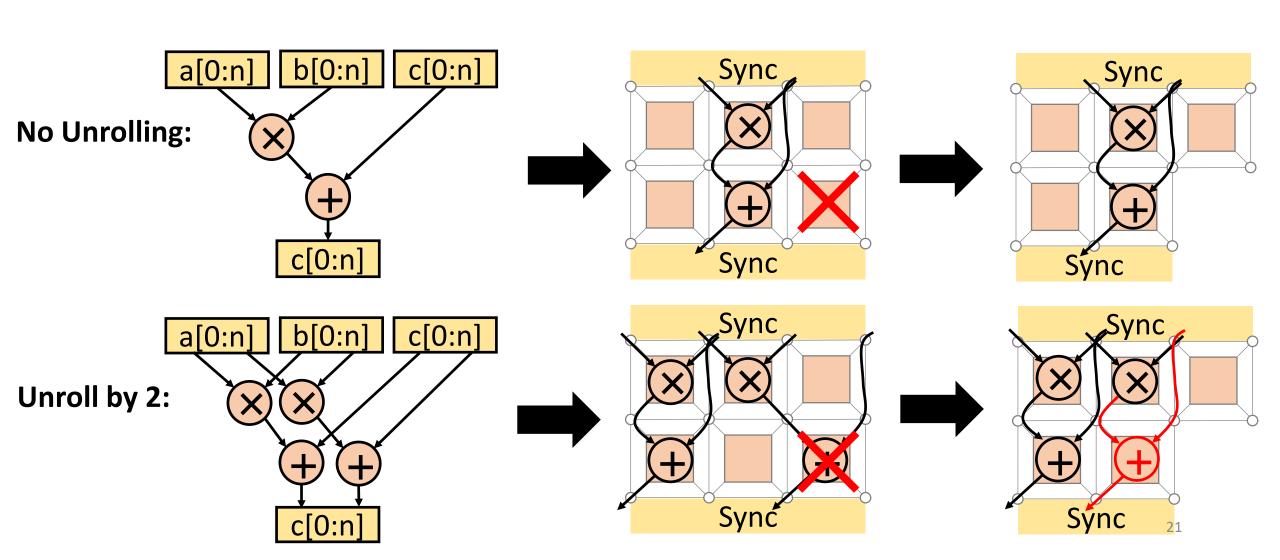

### Repairing the Spatial Mapping

```

// Original Code

for (i=0; i<n; ++i)

c[i]+=a[i]*b[i];</pre>

```

#### Hardware/Software Interface Generation

- How to configure accelerator with arbitrary topology?

- Reuse the data path for configuration

- Find path(s) that cover(s) all the components

- A heuristic based heuristic algorithm to minimize the longest path of configuration

- For a graph with m nodes covered by n paths, the longest path cannot be shorter than  $\lceil \frac{m}{n} \rceil$ .

- We only introduces 40% overhead over the ideal bound.

#### Outline

- Decoupled-Spatial Architecture

- Compilation

- Design Space Exploration

- Evaluation

- Methodology

- Compiler

- Design Space Exploration

## Methodology

#### Performance

- Gem5 RISCV in-order core integrated with a cycle-accurate spatial accelerator simulator

- The in-order core is extended with stream decoupled ISA

#### • Power/Area

- All the components are implemented in Chisel RTL

- Synthesized in Synopsys DC 28nm @1.00GHz

- SRAM power/area are estimated by CACTI 7.0

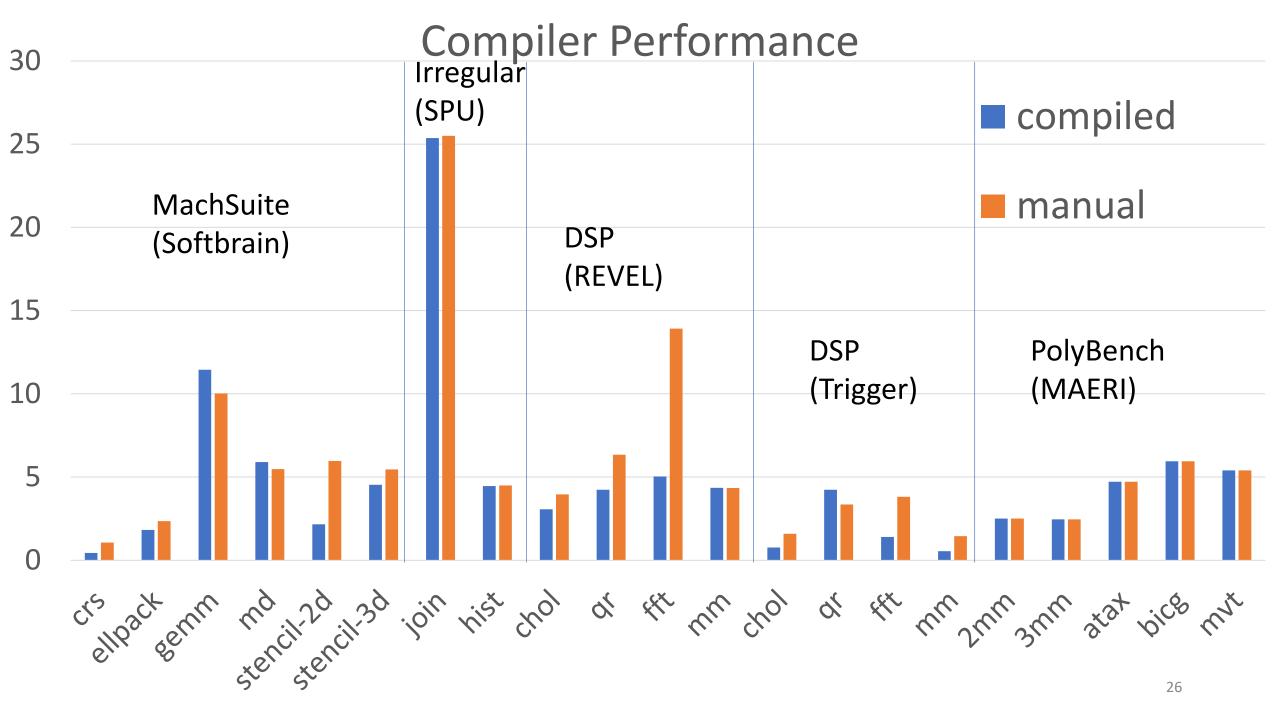

#### Compiler Performance

- Softbrain MachSuite

- Versatile accelerator can handle moderate irregularity

- SPU Histogram, and Key Join

- Accelerator specialized for irregular workloads

- REVEL and Trigger DSP

- Accelerator specialized for imperfect loop body

- MAERI PolyBench

- Accelerator for neural network

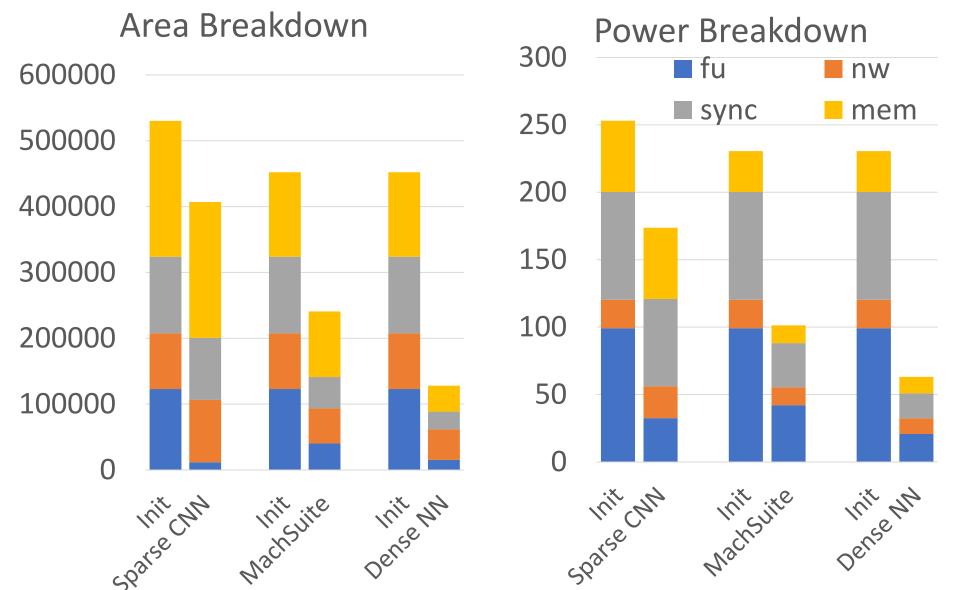

## Design Space Explorer

- Workloads

- Dense Neural Network

- MachSuite

- Sparse Convolutional Neural Network

- Initial Design

- A 5x5 mesh with all capability (arithmetic, control, and indirect)

- Objective: perf<sup>2</sup>/mm<sup>2</sup>

# Design Space Explorer

Sparse CNN: 24h

MachSuite: 19.2h

Dense NN: 16h

# Conclusion

|              | HLS                             | Manual                       | DSAGEN                               |

|--------------|---------------------------------|------------------------------|--------------------------------------|

| Frontend     | C+Pragma                        | DSL/Intrinsics, etc.         | C+Pragma                             |

| Design Flow  | Nearly Automated                | Manual                       | Nearly Automated                     |

| Input        | A <b>Single</b><br>Application  | Multiple Target Applications | Multiple Target<br>Applications      |

| Output       | Application-<br>Specific Accel. | ASIC/Programmable Accel.     | A <b>Programmable</b><br>Accelerator |

| Design Space | Limited                         | Rich                         | Rich                                 |

#### Q&A

- Our framework is working in progress at: https://github.com/PolyArch/dsa-framework

- All the questions and comments are welcomed